動作確認

Vivado 2015.4 on Windows 8.1 pro (64bit)

DIGILENT ZYBO

http://qiita.com/7of9/items/fd8c6a7c329f130ab7c9#%E6%9C%AA%E6%B6%88%E5%8C%96

においてClockCounterのResetの周期をClk周期の16倍とした時に4ビット表示用LEDのMSB相当が点灯しなかった。

code v0.1 > MSBが点灯しないバージョン

VHDLとテストベンチを作って同じ状況を確認した。

clockCounter2.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity counter is

port( Clk : in std_logic;

Reset : in std_logic;

OUT_D : out std_logic_vector (3 downto 0)

);

end counter;

architecture Behavior of counter is

signal DFF_8 : std_logic_vector (3 downto 0);

begin

process(Clk, Reset)

begin

OUT_D <= DFF_8;

if (Reset = '1') then

DFF_8 <= (others => '0');

elsif ( clk'event and clk = '1') then

if (DFF_8 = "1111") then

DFF_8 <= (others => '0');

end if;

DFF_8 <= DFF_8 + 1;

end if;

end process;

end Behavior;

clockCounter2.tb

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity testbench is

end testbench;

architecture behavior of testbench is

signal clk : std_logic;

signal reset : std_logic;

signal out_d : std_logic_vector (3 downto 0);

constant clk_period : time := 10 ns;

begin

uut: entity work.counter PORT MAP (

clk => clk,

reset => reset,

out_d => out_d);

stimulus : process

begin

wait for 16 * clk_period / 2;

reset <= '1';

wait for 16 * clk_period / 2;

reset <= '0';

-- wait for 300 ns;

end process;

clk_process : process

begin

clk <= '0';

wait for clk_period / 2;

clk <= '1';

wait for clk_period / 2;

end process;

end behavior;

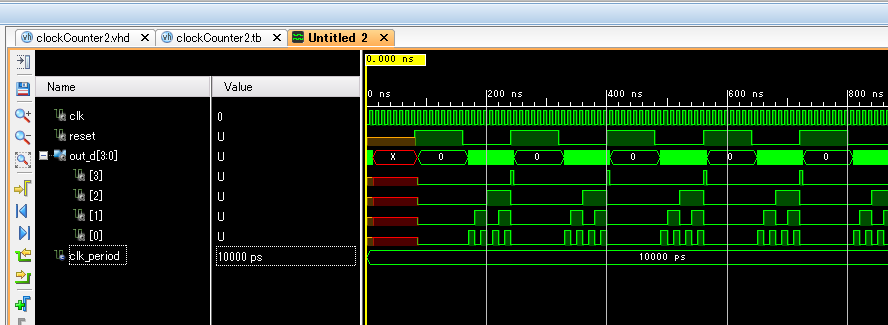

ResetのタイミングによってMSB (out_d[3])が短時間しかHレベルにならず、リセットがかかてしまっていることが確認できた。

ResetピンがLレベルの間に4ビットすべてが処理されないといけないということか。

そうなると16分周でなく32分周が必要になるということに整合性が取れるようだ。

code v0.2 > MSBも点灯するバージョン

テストベンチだけを16分周から32分周に変更した。

clockCounter2.tb

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity testbench is

end testbench;

architecture behavior of testbench is

signal clk : std_logic;

signal reset : std_logic;

signal out_d : std_logic_vector (3 downto 0);

constant clk_period : time := 10 ns;

begin

uut: entity work.counter PORT MAP (

clk => clk,

reset => reset,

out_d => out_d);

stimulus : process

begin

-- wait for 16 * clk_period / 2;

wait for 32 * clk_period / 2;

reset <= '1';

-- wait for 16 * clk_period / 2;

wait for 32 * clk_period / 2;

reset <= '0';

-- wait for 300 ns;

end process;

clk_process : process

begin

clk <= '0';

wait for clk_period / 2;

clk <= '1';

wait for clk_period / 2;

end process;

end behavior;

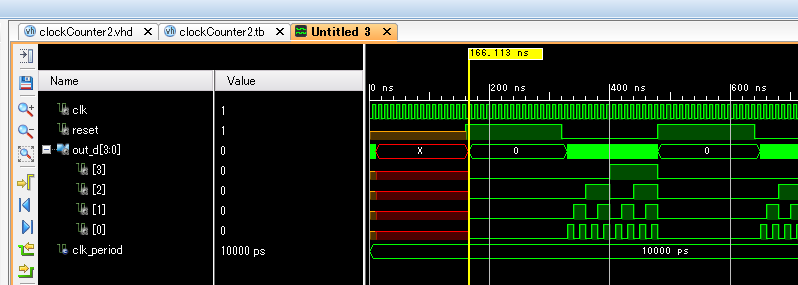

ResetピンがLレベルの間に4ビットのカウントがすべて処理されるようになった。

ResetピンがHレベルの時間が長いかもという問題は将来の課題としておく。