動作確認

Windows 10 Pro (v1909)

PYNQ-Z1 (Digilent) (以下、PYNQと表記)

PYNQ v2.5 Image

Vivado v2019.1 (64-bit)

概要

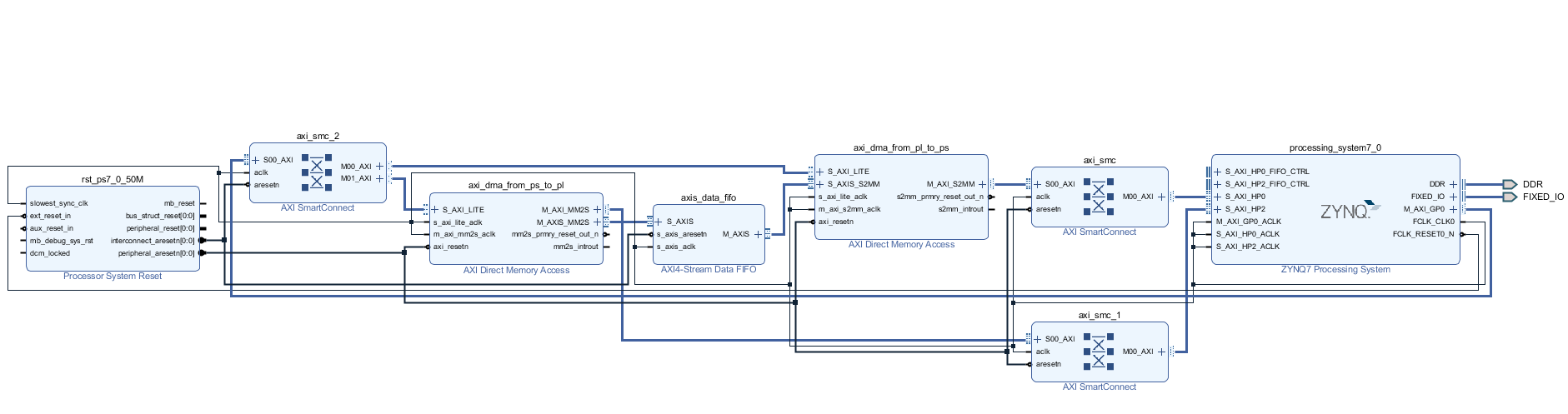

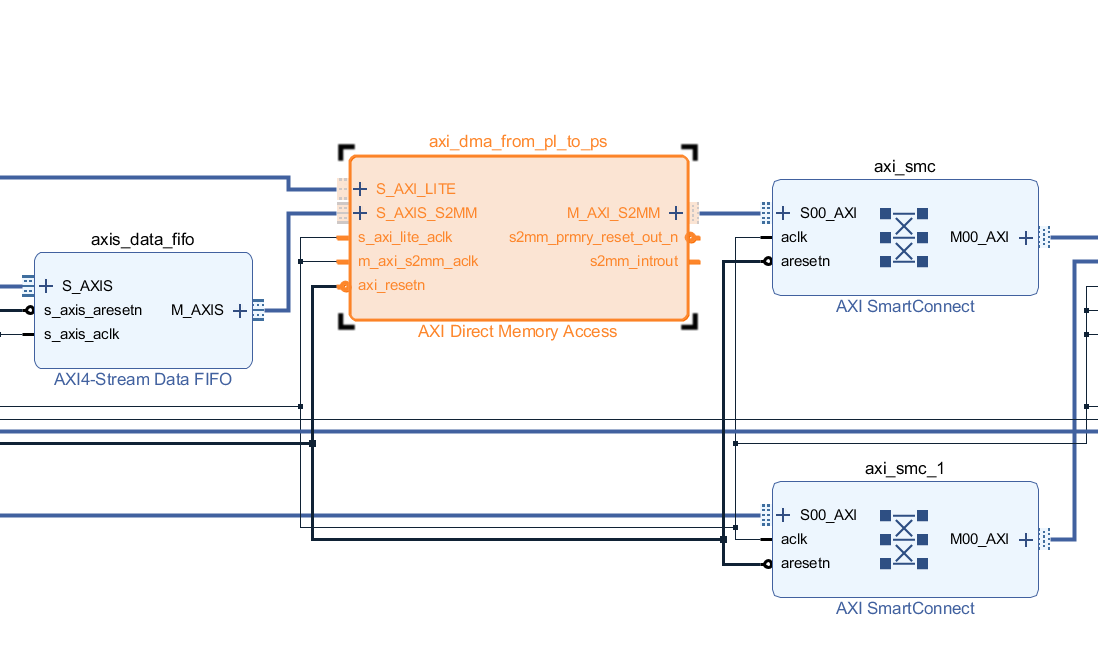

- PYNQ_Workshopにて掲載されているDMAの実装を試した

- 二つのDMA (read, write) + FIFO

- 提供される.bitと.tclでの動作

- Vivado 2019.1で.bitと.tclを生成した上での動作

- Block Designの設定

PYNQ Image

- PYNQ v2.5 Imageを使用

- Glasgow Release のPYNQ-Z1 v2.5 SDCard image

提供される.bitと.tclでの動作

dma_tutorial.bitとdma_tutorial.tclを/home/xilinx/jupyter_notebooks/base/にscp。

from pynq import Overlay

overlay = Overlay("/home/xilinx/jupyter_notebooks/base/dma_tutorial.bit")

上記のようにoverlayを用意して、あとはTutorial通りに実行。

https://github.com/Xilinx/PYNQ_Workshop/blob/master/Session_4/6_dma_tutorial.ipynb

Vivado 2019.1で.bitと.tclを生成した上での動作

- dma_tutorial.bitとdma_tutorial.tclを任意のフォルダにコピー

- 例:

C:\pynq_proj_2020-05-23\2020-08-01_1010_DMATutorial\dma_tutorial

- 例:

- Vivado v2019.1を起動

- tclコンソールにて

- cd C:/pynq_proj_2020-05-23/2020-08-01_1010_DMATutorial/dma_tutorial

- source dma_tutorial.tcl

Block Designが生成される。

bitstream生成までは8分41秒かかった (Core i7-6700K 4.00GHz + 16GB RAM)。