動作環境

- Windows 10 Pro (21H1)

- Vivado 2019.1

概要

AXI IICに関してレジスタアクセスで操作をしたい。PS側からレジスタアクセスをしている例はあるが、それをPL側から実施したい。

PL側から実施するためにはAXIの通信を実装することになる。AXIの実装そのものは複雑であるため、簡単にする方法を探していたところ、良い資料を見つけた。

-

シミュレーション用の Master を作成する

- 筑波大学 武内修 様

この動作の理解をするために上記の実装をAXI GPIOに対して実施してみた。

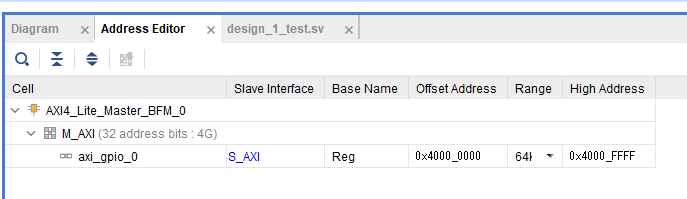

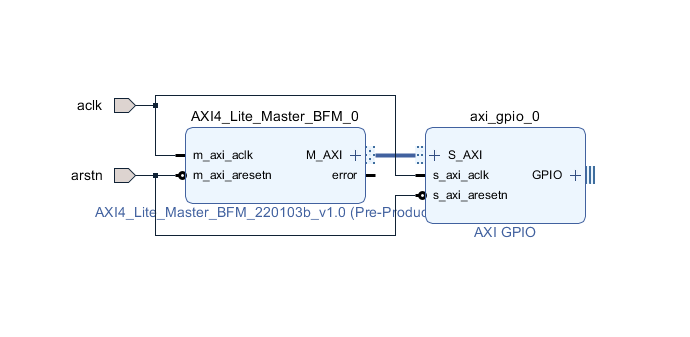

Block Design

記事に従い作成したAXI4_Lite_Master_BFMのIPとAXI GPIOを追加した。

テストベンチ

記事のテストベンチのうち、以下を変更した。

- デザインの名前がdesign_2ではなくdesign_1である

design_1 uut (.*);

- レジスタ0に0x01を書き込む

- レジスタ0に0x00を書き込む

design_1_test.sv

`timescale 1ns / 1ps

module design_1_test();

reg aclk = 0;

reg arstn = 0;

design_1 uut (.*);

// detect error

always @(posedge uut.AXI4_Lite_Master_BFM_0.inst.error)

$display("AXI4 error @ %t", $time);

// generate clock

always #5 aclk <= !aclk;

initial begin

repeat(10) @(posedge aclk);

arstn <= 1;

repeat(10) @(posedge aclk);

uut.AXI4_Lite_Master_BFM_0.inst.write(0, 'h0001);

repeat(10) @(posedge aclk);

uut.AXI4_Lite_Master_BFM_0.inst.write(0, 'h0000);

repeat(10) @(posedge aclk);

repeat(10) @(posedge aclk);

$stop;

end

endmodule

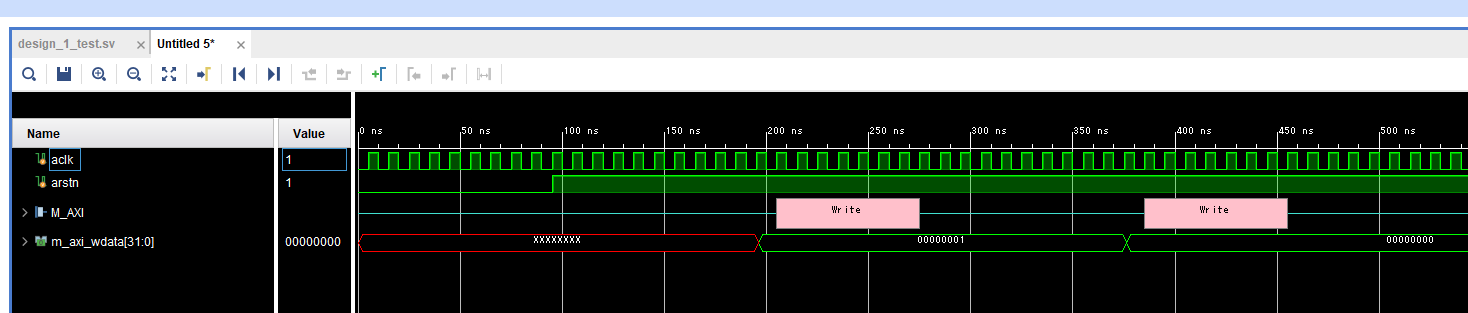

Run Simulation

0x00と0x01がAXIで書き込まれることを確認できた。

留意点: Make Externalしていない

AXI GPIOのGPIOポートをMake Externalしていない。

Make Externalすると、Run Simulation時に以下のエラーになる。

elaborate.log

...

ERROR: [VRFC 10-2996] 'GPIO_0_tri_i' is not found for implicit .* port connection [C:/coraZ7prj_201016/testing_axi4_lite/testing_axi4_lite.srcs/sim_1/new/design_1_test.sv:8]

ERROR: [XSIM 43-3322] Static elaboration of top level Verilog design unit(s) in library work failed.

このため、上記ではGPIOポートをMake Externalしていない。

Note: この問題はいますぐ解決が必要でないため、保留としている。必要になった時に調べる。

関連

以下にもサンプルがある。こちらの場合はAR#37425から取得できるaxi_master.vを使っているようだ。

- FPGAプログラミング大全 Xilinx編 第2版 p366

- 小林優 様