そろそろプログラマーもFPGAを触ってみよう!

これはbuilderscon tokyo 2016の発表スライドです。

自己紹介

- クラウドのデベロッパー・アドボケイト

- エバンジェリストみたいなお仕事

- コミュニティ支援:GCPUG、bq_sushi、TensorFlow User Group etc

- 趣味のFPGA

- 2013年くらいからいじり始め

- FPGAエクストリーム・コンピューティング主宰:合計8回

これまでに書いたFPGA記事

はてなブックマークでバズった記事たち

- マイクロソフトはどうやってBingをFPGAで実装したか: 952 users

- ハード素人が32bit CPUをFPGAで自作して動かすまで読んだ本のまとめ: 576 users

- 文字通り「ネットワークがコンピューター」な金融HFTでのFPGAの使われ方: 517 users

- JP Morgan Chaseがデリバティブ専用スパコンをFPGAで作った話: 285 users

FPGAをめぐる最近の動き

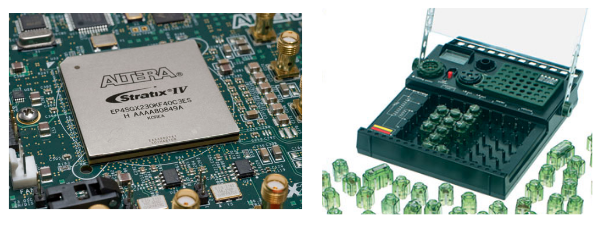

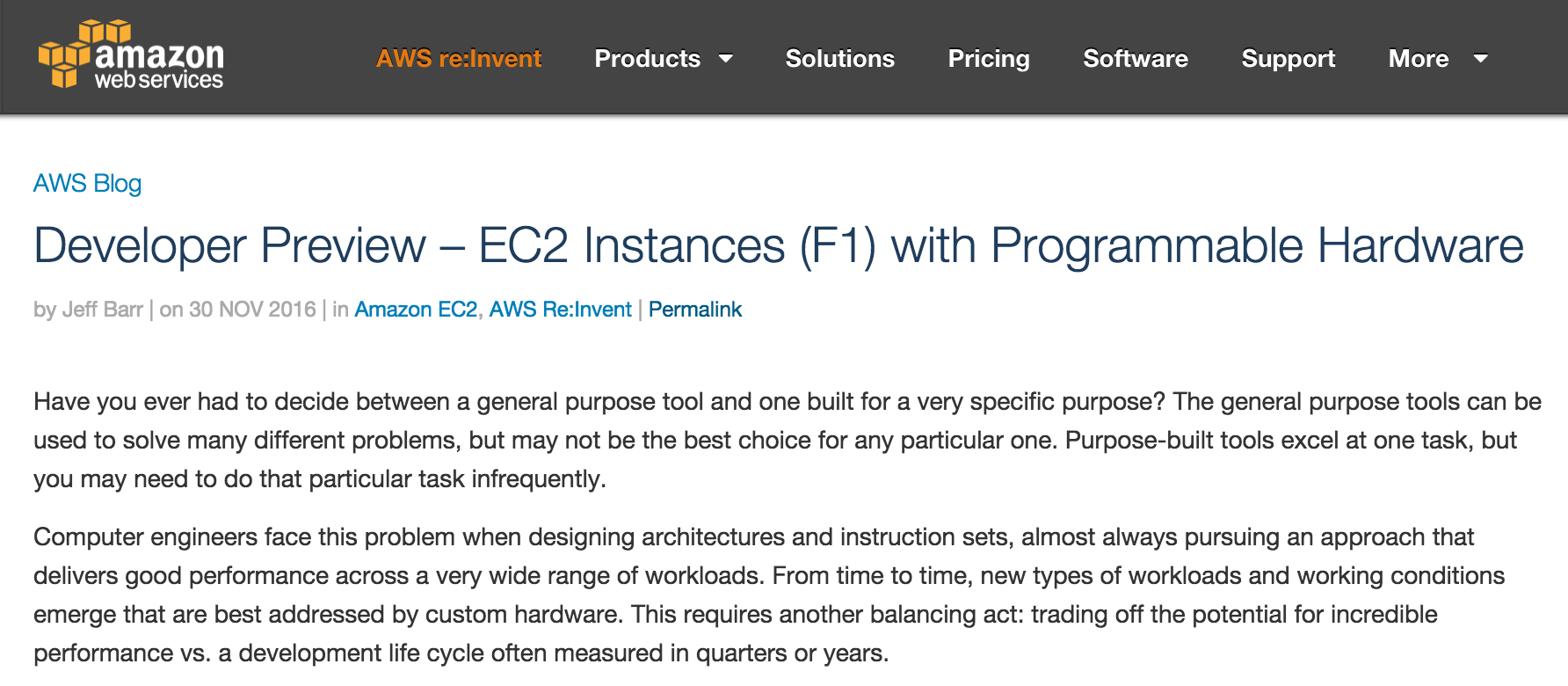

AWS、FPGAインスタンス提供開始

わお

From: https://aws.amazon.com/blogs/aws/developer-preview-ec2-instances-f1-with-programmable-hardware/

From: https://aws.amazon.com/blogs/aws/developer-preview-ec2-instances-f1-with-programmable-hardware/

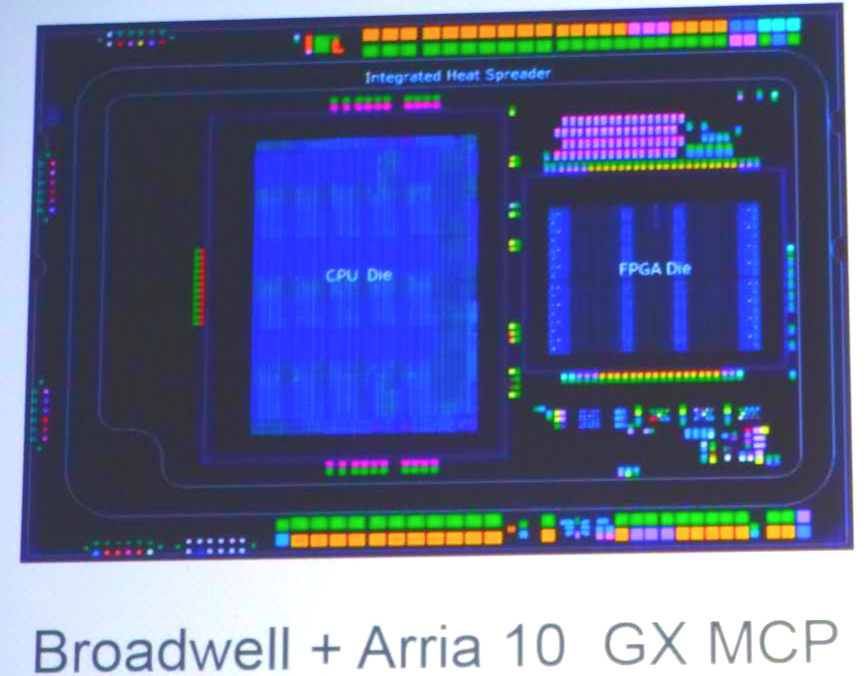

Intel、FPGAを大人買い

1年前にFPGA大手Alteraを2兆円で買収

Xeon+FPGAチップは2017年出荷

From: https://www.nextplatform.com/2016/03/14/intel-marrying-fpga-beefy-broadwell-open-compute-future/

From: https://www.nextplatform.com/2016/03/14/intel-marrying-fpga-beefy-broadwell-open-compute-future/

「2020年までにクラウドサーバの1/3はFPGAを導入」

ニューラルネット、暗号化、データ圧縮など

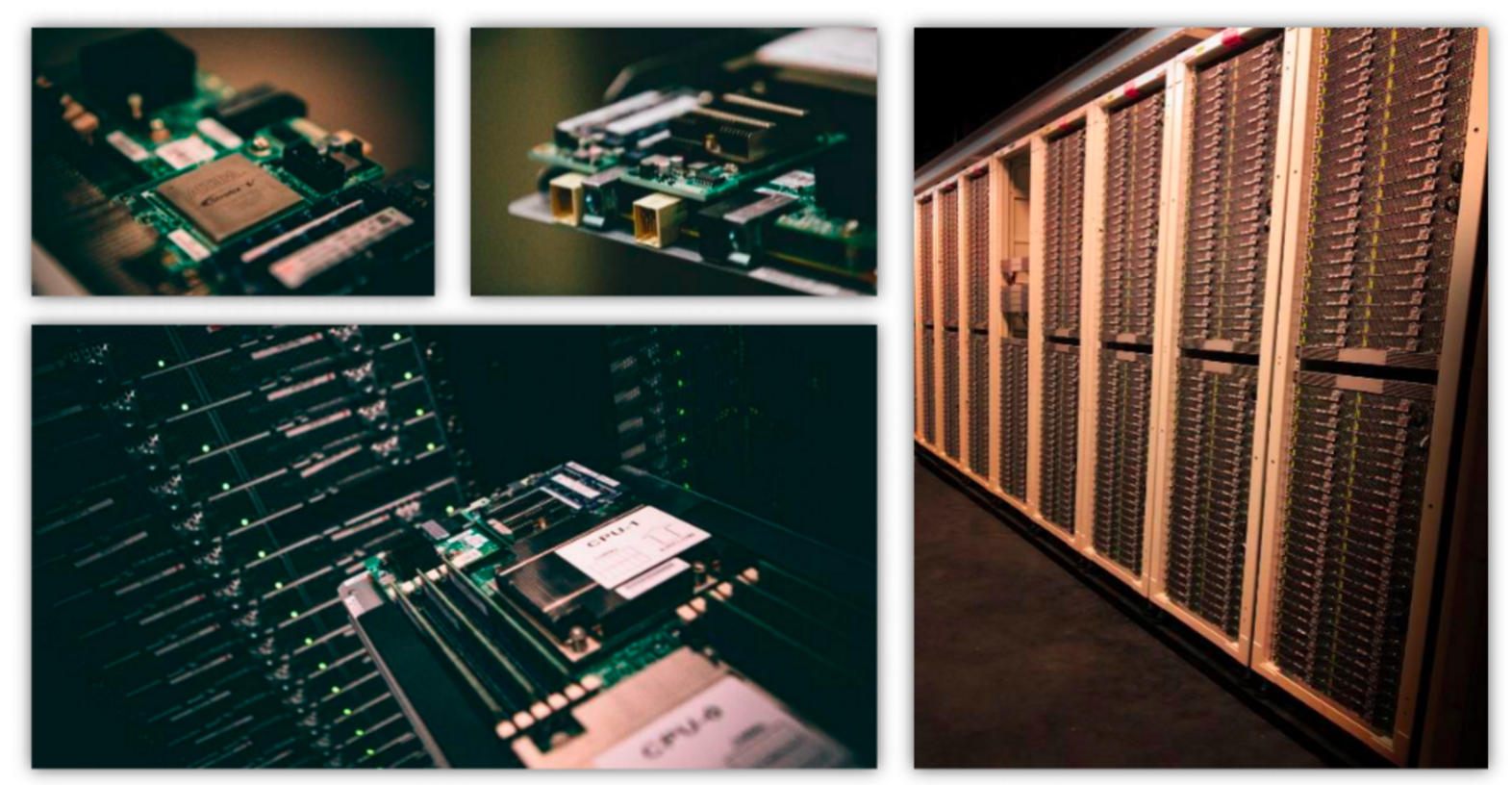

MicrosoftもFPGAに賭けてる

「Microsoftのデータセンターの新規サーバは、ほぼすべてにFPGAを搭載」

From: https://www.microsoft.com/en-us/research/project/project-catapult/

From: https://www.microsoft.com/en-us/research/project/project-catapult/

IBMもFPGA

IBMのクラウドサービスでFPGAをホスティング

From: http://www.electronicsweekly.com/news/xilinx-and-ibm-put-big-data-fpga-design-in-the-cloud-2016-04/

From: http://www.electronicsweekly.com/news/xilinx-and-ibm-put-big-data-fpga-design-in-the-cloud-2016-04/

FPGA使うとどうなる?

MicrosoftのBing検索

Webページの特徴量抽出とニューラルモデル推論をFPGA実装

スループットが2倍に

From: http://qiita.com/kazunori279/items/6f517648e8a408254a50

From: http://qiita.com/kazunori279/items/6f517648e8a408254a50

Azureの翻訳サービス

CPUは14秒→FPGAは2.6秒

From: http://japan.zdnet.com/article/35089622/2/

From: http://japan.zdnet.com/article/35089622/2/

JP Morgan

デリバティブのリスク分析をFPGA実装に移植

全社規模のリスク分析が8時間から4分に

From: http://d.hatena.ne.jp/kazunori_279/20130903/1378160380

From: http://d.hatena.ne.jp/kazunori_279/20130903/1378160380

IBM Netezza

データウェアハウス・アプライアンス

SQLクエリをFPGA搭載のI/Oコントローラで処理、鬼速

From: https://thinkit.co.jp/article/1161/1

From: https://thinkit.co.jp/article/1161/1

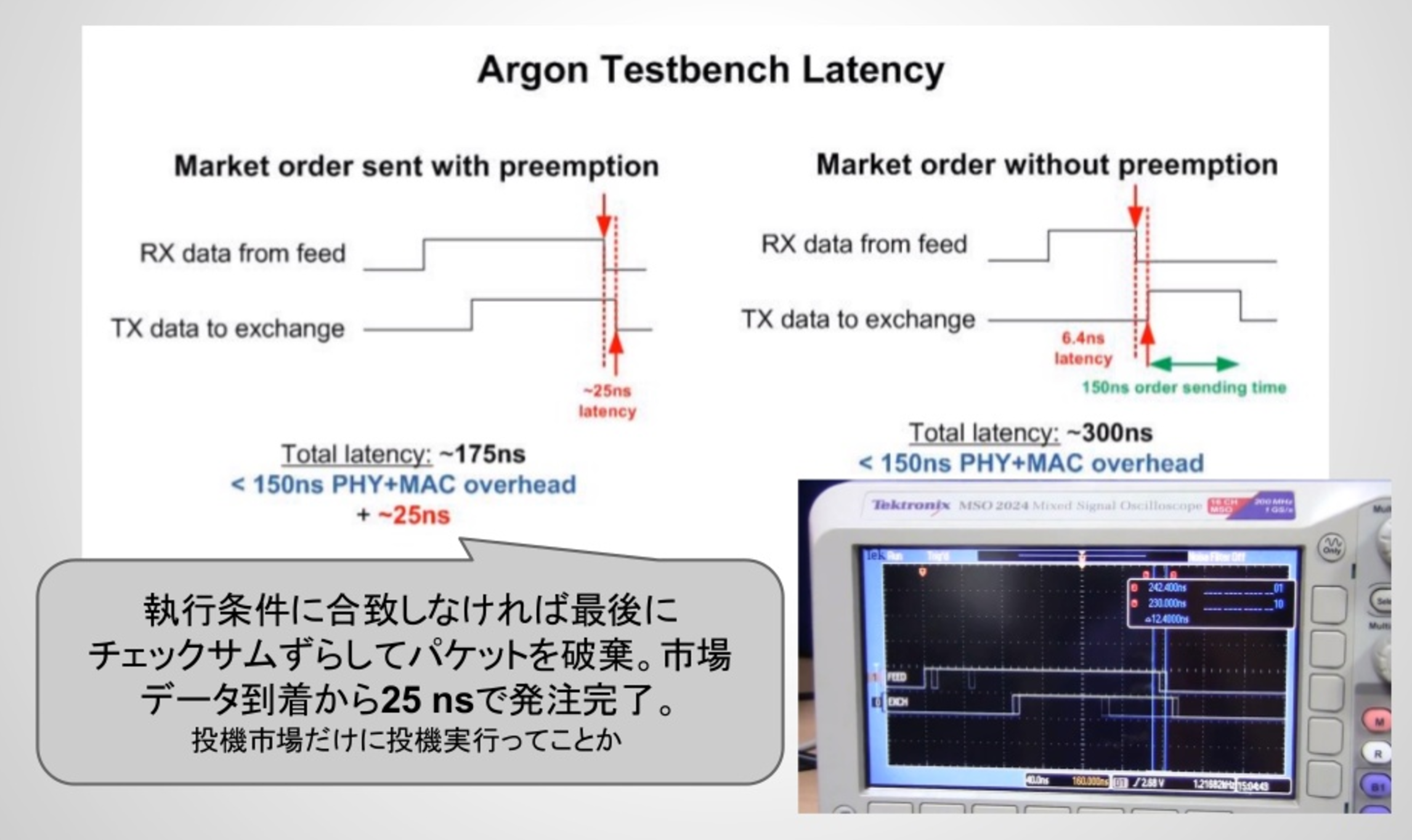

25 nsで株価取引

High Frequency Trading (HFT):マイクロ秒単位で売買。ソフトでは間に合わない

株価パケットの受信中に売買パケットを送り始める(意味不明)

From: http://www.slideshare.net/kazunori279/moving-computation-to-the-data-1

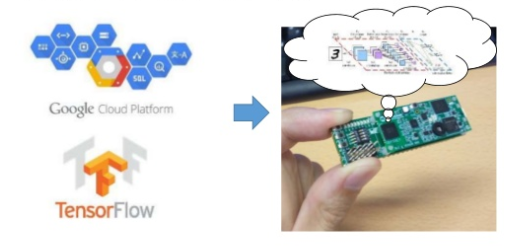

ニューラルネットもFPGAで

東工大・中原先生がさくっと作った事例

CNNで画像認識:RasPiのARMでは85.81 ms→FPGAでは1.56 ms

消費電力もひと桁くらい低い。電力性能比はたぶん二桁くらいの差

From: http://www.slideshare.net/HirokiNakahara1/tensor-flow-usergroup-2016

From: http://www.slideshare.net/HirokiNakahara1/tensor-flow-usergroup-2016

なぜいまFPGAか?

ムーアの法則は終わった

CPUクロックは数GHzどまり。コア数増えても活用は限定的

特定用途向けの専用設計ハードウェア、アクセラレータでがんばるしか

From: http://research.microsoft.com/pubs/212001/Catapult_ISCA_2014.pdf

From: http://research.microsoft.com/pubs/212001/Catapult_ISCA_2014.pdf

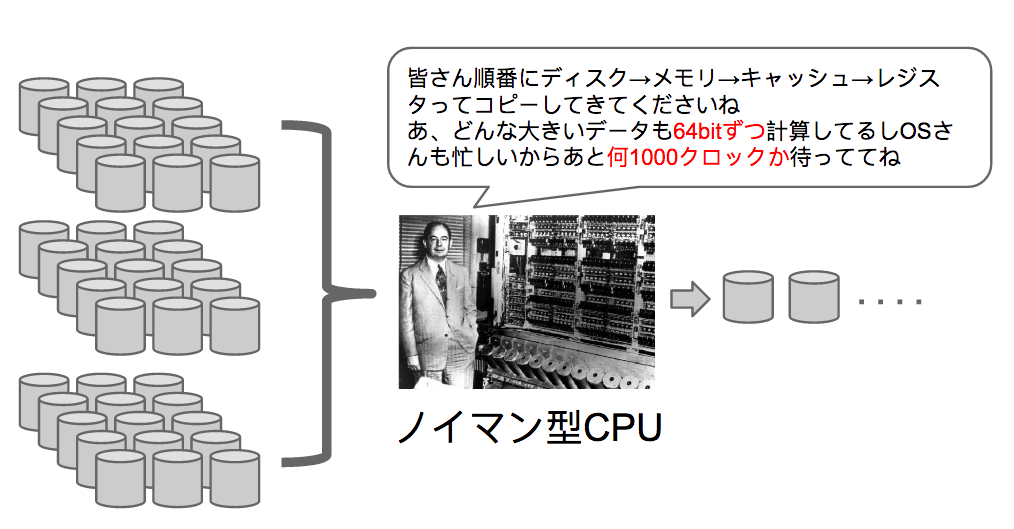

そもそもノイマン型ってどうなの

ボトルネックじゃね?

シリコンダイの大半がキャッシュで埋まる

演算器あまり並べられない

ではCPU以外の選択肢は?

以下はおおざっぱな印象

適材適所が肝要

| ◯ | × | |

|---|---|---|

| CPU | ソフト開発者たくさん。クロック最速(数GHz) | 汎用品の限界。ノイマンボトルネック。クロックもう伸びない |

| GPU | 大量の数値演算なら最強。ソフト開発者が扱える。クロック速い(1GHz位) | 汎用品の限界。電力食い過ぎ(200W) |

| ASIC | 自由に専用設計できる。低消費電力(uW〜W) | 修正できないので開発が大がかり。1〜2年+数億円かかる。コストの8割が検証作業 |

| FPGA | 自由に専用設計できる。低消費電力(mW〜W)。いつでも仕様変更・バグ修正できる。1万円で試せる手軽さ | ソフト開発者には難しい。クロック遅い(数100MHz)。集積度低い |

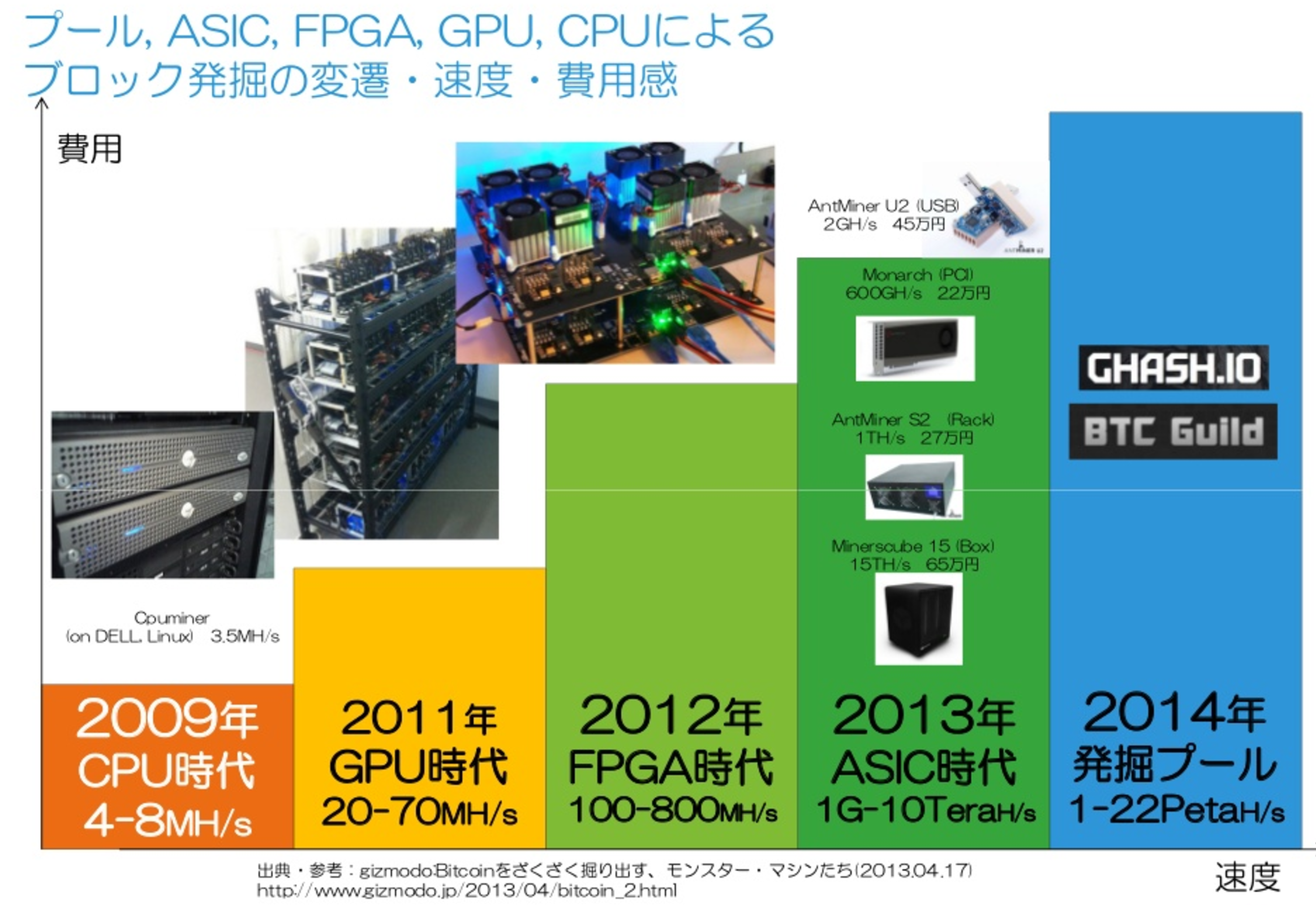

例:ビットコイン

ハッシュ値の総当りってFPGA/ASIC向き

From: http://www.slideshare.net/kenjiurushima/20140602-bitcoin1-201406031222

From: http://www.slideshare.net/kenjiurushima/20140602-bitcoin1-201406031222

FPGAって何?

Field Programmable Gate Array

デジタル回路を自分で設計できるLSI

つまり大人の電子ブロック。数万〜数百万個(値段相応)

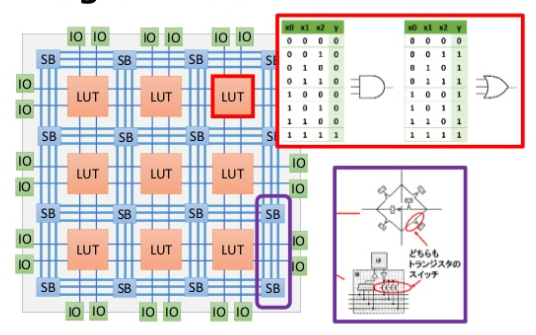

FPGAのしくみ

論理ゲートの動作や接続の状態をSRAMで持ってる

ソフトに近い手軽さでハードを設計。バグっても直せる

From: http://www.slideshare.net/HirokiNakahara1/tensor-flow-usergroup-2016

From: http://www.slideshare.net/HirokiNakahara1/tensor-flow-usergroup-2016

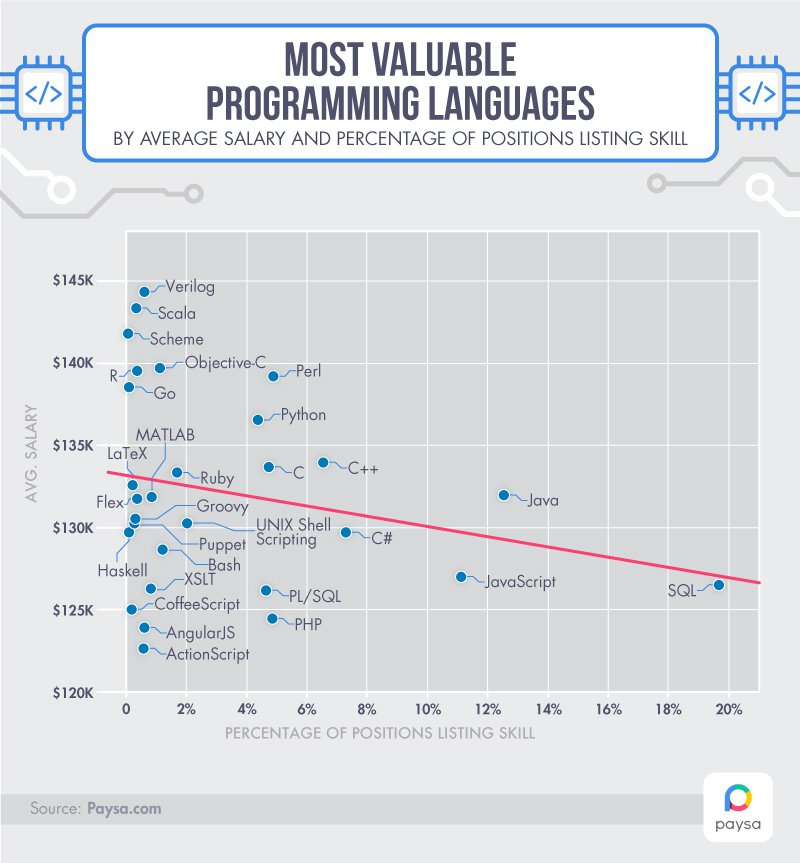

デジタル回路をHDLで書く

Hardware Description Language (HDL)

- Verilog HDLとVHDLが主流

- 光の速さ(数10ns)で動くExcelの式みたい

assign X = A & B | ~C;

これが、こうなる

From: http://monoist.atmarkit.co.jp/mn/articles/0809/04/news122.html

HDL書けるとモテるらしい

From: http://news.mynavi.jp/news/2016/11/30/101/

From: http://news.mynavi.jp/news/2016/11/30/101/

HDLをビルドして、FPGAに流すと動く

From: http://www.slideshare.net/HirokiNakahara1/tensor-flow-usergroup-2016

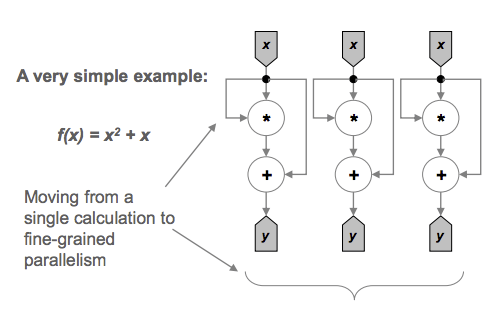

FPGAの得意なこと

特定用途向けの並列計算機をお手軽に作れる

例:1000個のデータに対して「x^2 + x」を計算したい

ループなんていらない。演算器を1000個並べればいいさ

OSのスレッド切替のオーバーヘッドなし。数クロックで完了

From: http://www.stanford.edu/class/ee380/Abstracts/110511-slides.pdf

From: http://www.stanford.edu/class/ee380/Abstracts/110511-slides.pdf

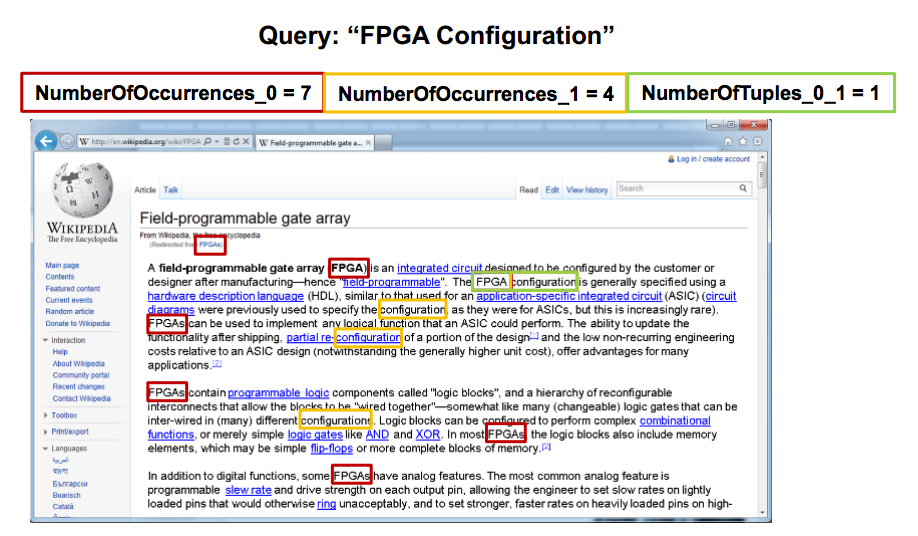

たとえばMicrosoft Bingでは

こんなWebコンテンツの特徴量抽出をソフトでやると600μsかかってた

From: http://qiita.com/kazunori279/items/6f517648e8a408254a50

From: http://qiita.com/kazunori279/items/6f517648e8a408254a50

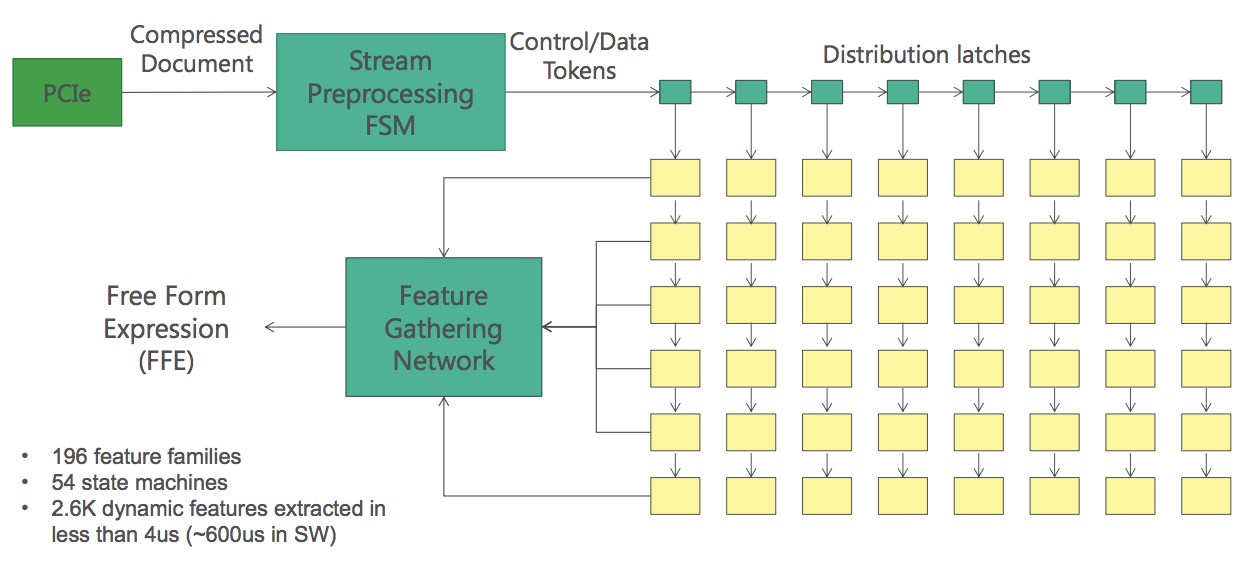

たとえばMicrosoft Bingでは

1つのWebコンテンツを54個のステートマシンに同時に流して並列に特徴量抽出

FPGA実装では処理時間が4μsに。150倍の高速化

From: http://qiita.com/kazunori279/items/6f517648e8a408254a50

From: http://qiita.com/kazunori279/items/6f517648e8a408254a50

パイプライン処理・ストリーム処理が得意

大規模整数演算、パターンマッチ、暗号化、フィルタリング等々

いちいちメモリ読み書き不要。内蔵SRAMが鬼速(数TB/s)

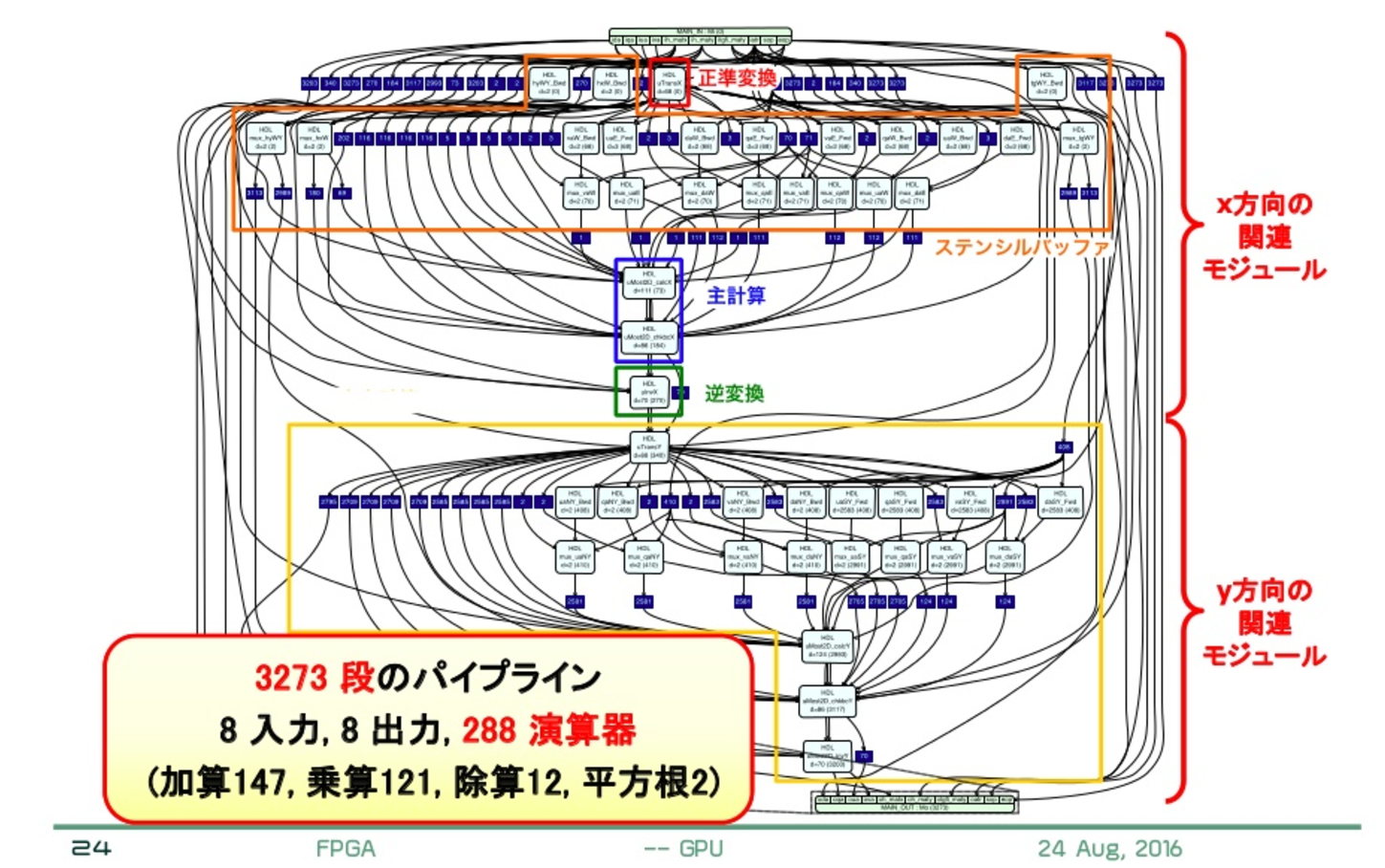

東北大・佐野先生の津波シミュレーション:

3000段のパイプラインを組んでGPUに勝った

From: http://www.slideshare.net/KentaroSano/fpga-gpu

From: http://www.slideshare.net/KentaroSano/fpga-gpu

俺たちの知らない非ノイマン型の世界

ハードウェアアルゴリズム

クイックソートが最速ではない世界。ソートネットワークならO(log n)

シストリックアレイ、データフローなどなど。FPGAの原理と構成を読むべし

JOINやソート、ストリーム処理の専用並列計算機を自作できる

FPGAが向かない用途

- 大きなデータにランダムアクセスするもの

- 内部のSRAMに収まる演算なら激速

- 収まらないとDRAMアクセス発生して遅い

- そもそも並列化の難しい処理

- クロック遅いので逐次処理はCPUにかなわない

- ソフトやGPUでさっさと用が済む用途

- FPGA開発のコストと天秤

- いずれASICに乗っ取られる用途

- 大量の需要が見込め、ASIC開発がペイするもの

- 仕様が年単位で固定(決まった積和演算とか)

FPGAを使ってみよう

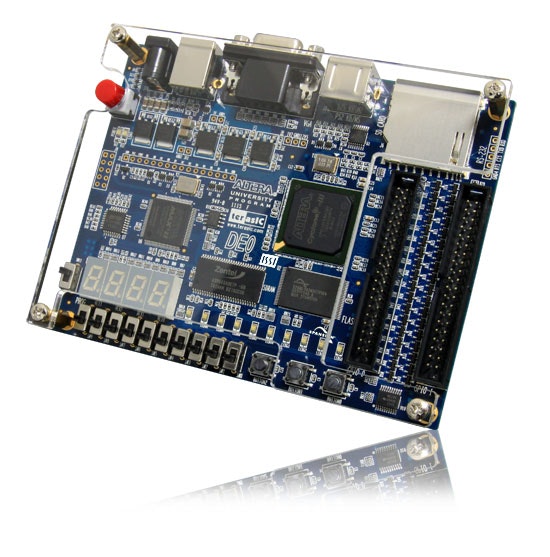

安いFPGAボードを買ってみた

クラウドFPGAもいいけど、RasPiみたいに電子工作するの楽しい

DE0で1万5千円くらい。入門書も買った

From: http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=364

From: http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&No=364

まずは音を鳴らしてみる

Verilog HDLでカウンタを書く(詳細)

50MHzのクロックを数えて5万ごとにスピーカーをオンオフ

50M / 100K = 440Hzの音が鳴るはず

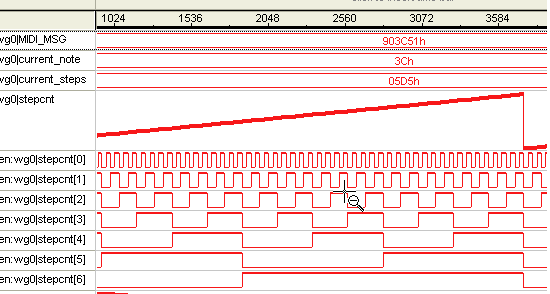

シミュレータで検証

なんかカッコいいぞ

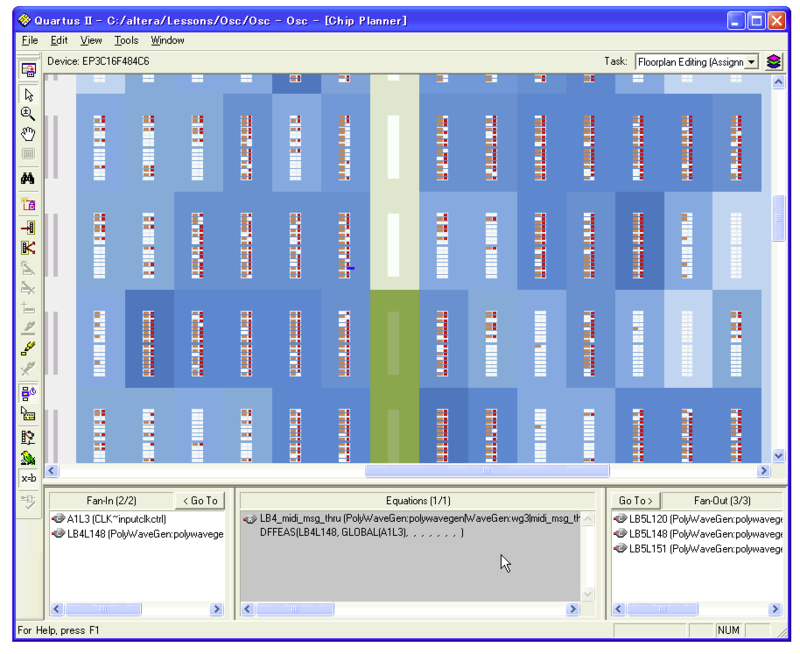

ベンダーツールでビルド

配線だのタイミングチェックだの、重い

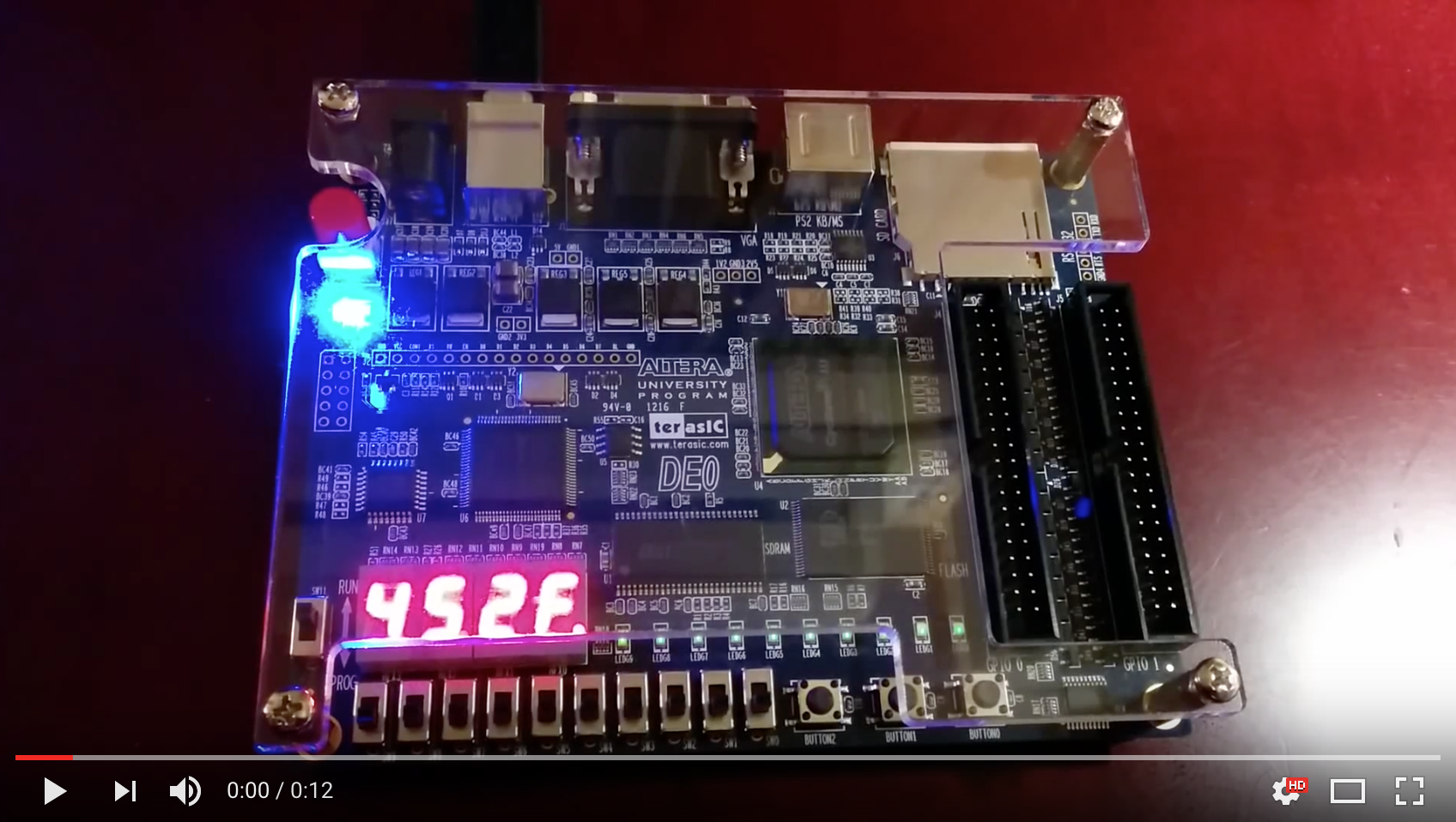

ビルドが終わったらDE0に流す

なったぜ!

From: https://www.youtube.com/watch?v=GFKxnQ_mz1c

From: https://www.youtube.com/watch?v=GFKxnQ_mz1c

キーボードにつないで和音も出た

- MIDIデコード→正弦波生成→エンベロープ制御(詳細)

From: https://www.youtube.com/watch?v=gahOvWER_8s

From: https://www.youtube.com/watch?v=gahOvWER_8s

キーボードのMIDIデータをFluentdに流してみた

- MIDIデコード→msgpackエンコード→TCPソケット

- CPUもOSもソフトもなしで、Fluentdを扱える(詳細)

From: https://www.youtube.com/watch?v=SEr9_NqvpBM

From: https://www.youtube.com/watch?v=SEr9_NqvpBM

32bitのMIPS CPUを作ってみた

- Cでfibを書いてgccでMIPSバイナリ生成、動いた(詳細)

From: https://www.youtube.com/watch?v=CamqAcVlJYQ

From: https://www.youtube.com/watch?v=CamqAcVlJYQ

...FPGA楽しい!

やってみてわかったこと:HDLを書くのは大変

- HDLは低レベルすぎて気が遠くなる

- 遊ぶのはいいけど、仕事で使うには検証作業が大変すぎる

- 全部をFPGA実装はムリなので、バス経由でCPU連携するの面倒

From: http://www.slideshare.net/HirokiNakahara1/tensor-flow-usergroup-2016

そこで高位合成だ

高位合成=High Level Synthesis (HLS)

ソフトウェア言語でハードのふるまいを記述、HDLを生成

先にソフトで動作チェックでき、検証作業がすっごくラク

- NECのCyber Work Bench:C言語。国内業界標準だけど高価すぎて俺には関係ない

- XilinxのVivado HLS:C/C++/System C。なんと最近無償化された!

- Intel (Altera)のFPGA SDK for OpenCL: C言語。OpenCLなのでGPUでも動く。ライセンスいくらだろう?

- みよしさんのSynthesijer:Java/Scala。オープンソース

- 高前田先生のPyCoRAM: 面倒なメモリアクセス部分をPythonで抽象化、肝心なところはHDLでガリガリ書ける。オープンソース

Synthesijerの例

こんなJavaコードを書くと...

From: http://www.sigemb.jp/ESS/2014/files/IPSJ-ESS2014003-1.pdf

From: http://www.sigemb.jp/ESS/2014/files/IPSJ-ESS2014003-1.pdf

Synthesijerの例

こんなHDLが出てくる

From: http://www.sigemb.jp/ESS/2014/files/IPSJ-ESS2014003-1.pdf

From: http://www.sigemb.jp/ESS/2014/files/IPSJ-ESS2014003-1.pdf

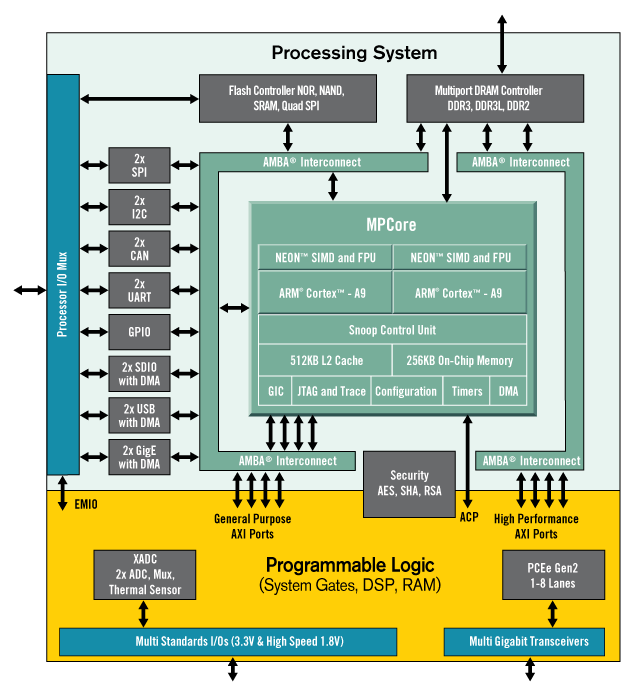

CPUとFPGAの連携は:SoCでラクしよう

System on Chip (SoC): CPUと周辺回路をワンチップに納めたもの

例: XilinxのZYNQ。デュアルコアARMとFPGAを混載、L2キャッシュを共有

From: https://japan.xilinx.com/products/silicon-devices/soc/zynq-7000.html

From: https://japan.xilinx.com/products/silicon-devices/soc/zynq-7000.html

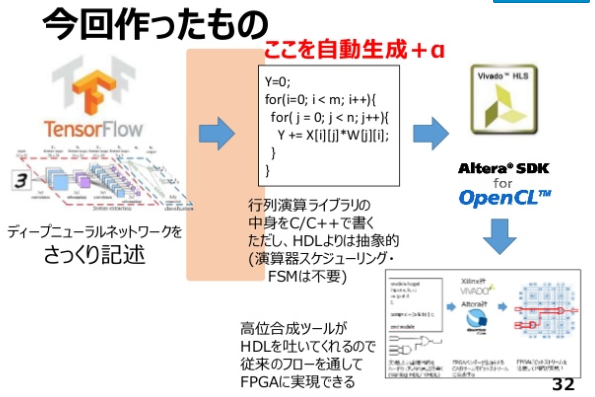

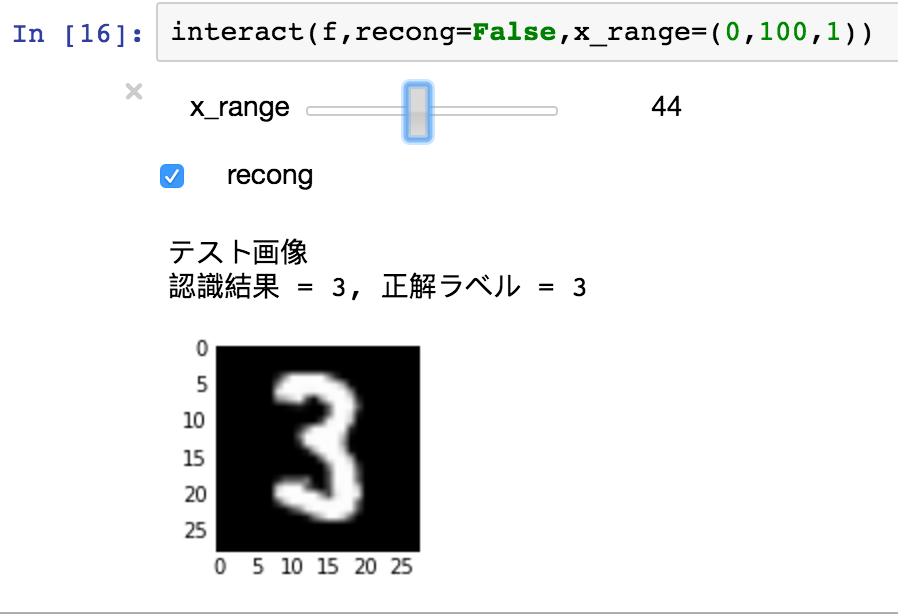

デモ

TensorFlow → Vivado HLS → HDL

ディープラーニング(CNN)による手書き数字文字認識(MNIST)

中原先生のTensorFlow高位合成デモをお借りしました。感謝です!

From: http://www.slideshare.net/HirokiNakahara1/tensor-flow-usergroup-2016

From: http://www.slideshare.net/HirokiNakahara1/tensor-flow-usergroup-2016

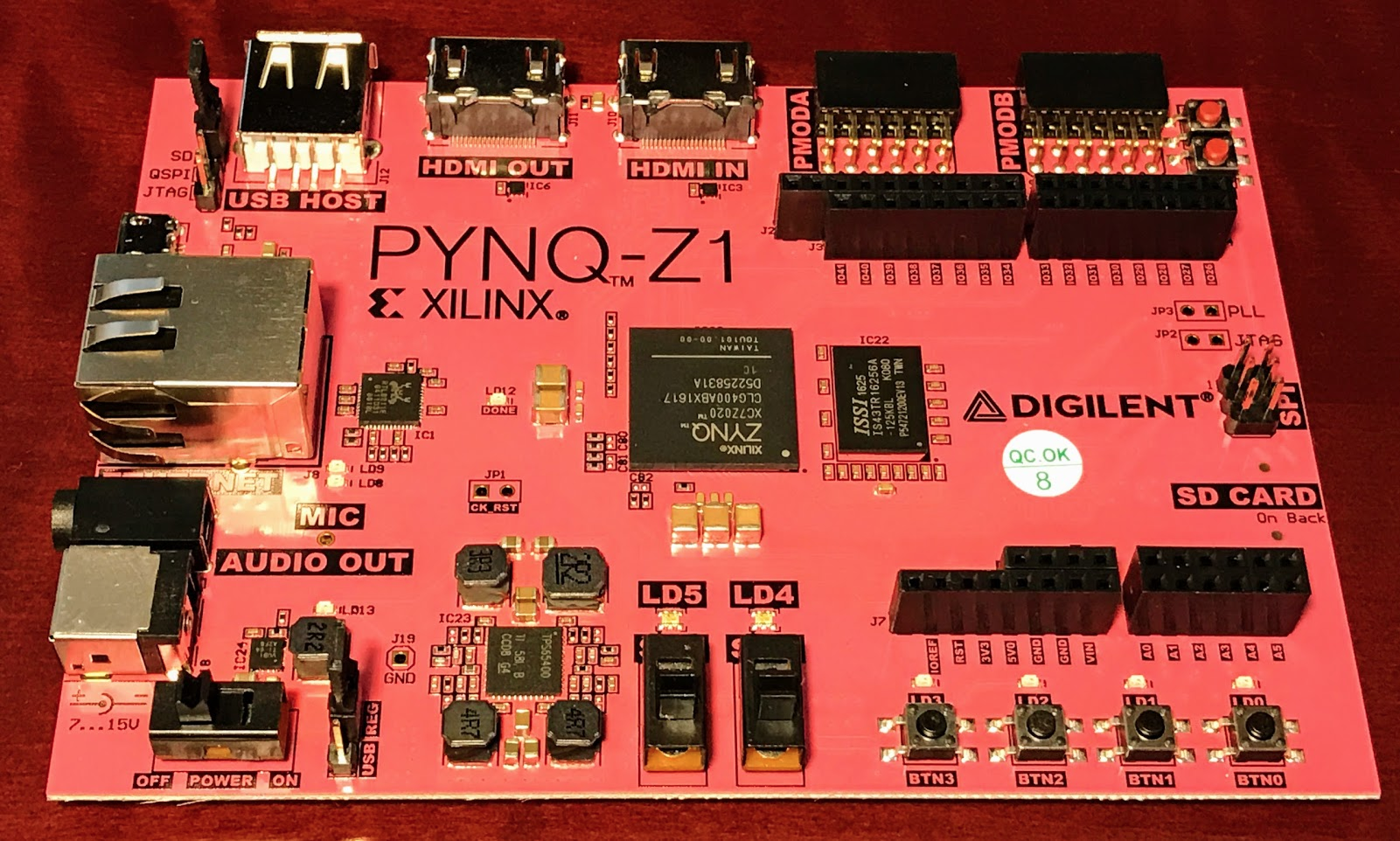

Xilinx PYNQで動かす

Xilinx PYNQ: ZYNQをPythonで手軽に使おう、というコンセプト

$229で買える。10日くらいで届いた

電源ONでARM上のLinuxを起動

Jupyter Notebookのサンプルコードで、あっという間にLチカ

JupyterでFPGA開発とは...Xilinxさん分かってらっしゃる

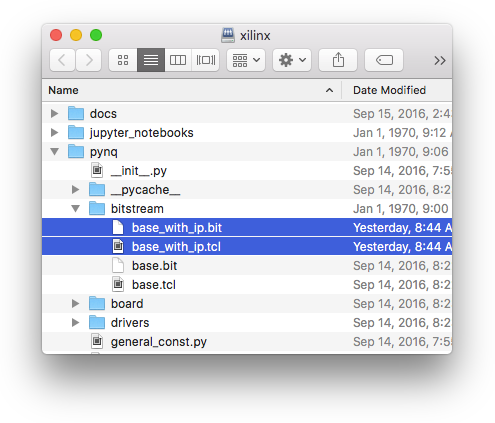

TensorFlowから生成したビットストリームをコピー

PYNQのフォルダをSMB経由で開いてドラッグ&ドロップ

なにこのお手軽さ。。

中原先生のNotebookもコピーして開く

これであとはNotebookをポチポチするだけ

FPGAにCNN回路を読み込み

# FPGAのハードウェア部(Programmable Logic(PL))にCNN回路を構成

from pynq import PL

from pynq import Overlay

# Vivado HLS (Cから高位合成)で生成した回路データを読み込み

# CNNのパラメータはTensorFlowで学習済み

# CNNの重みもあらかじめロードします

ol = Overlay("base_with_ip.bit")

ol.download()

PythonとFPGAのやりとり部分

手書き数字画像をFPGAのメモリ領域(0x1000)に書いて...

for i in range(0,784):

w = int(data[idx][i] * 256.0)

math_ip.write(0x1000+i*4,w) # MNISTのデータ転送

CNN回路を起動して認識

math_ip.write(0x0,0x01)

PythonとFPGAのやりとり部分

認識結果を読み出す

result=math_ip.read(0x0010)

結果を集計すると、認識率95%くらい

...

result = 6, label = 6

result = 5, label = 5

result = 8, label = 8

認識率 = 0.950000

なにこの手軽さ

Jupyterだからインタラクティブな可視化も得意

FPGAでの認識結果をぱらぱら表示

まとめ

FPGAおもしろいよ

- CPUに縛られないコンピューティング

- ハードなのに手軽に遊べる

- 高位合成やSoC、クラウドなど、環境も整ってきた

Disclaimer この記事は個人的なものです。ここで述べられていることは私の個人的な意見に基づくものであり、私の雇用者には関係はありません。