はじめに

フィボナッチを求める回路をVHDLとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)ではフィボナッチ回路はVHDLで記述しましたが、今回はJavaで記述してSynthesijerを使って高位合成したRTLを単体シミュレーションする例を示します。

用意するもの

- Xilinx Vivado 2015.3

- Synthesijer

- Ruby 1.9.3 以降

- Dummy_Plug 1.6.0

Dummy_Plug は AXI4/AXI4-Stream のBFM(バスファンクションモデル)ライブラリです。

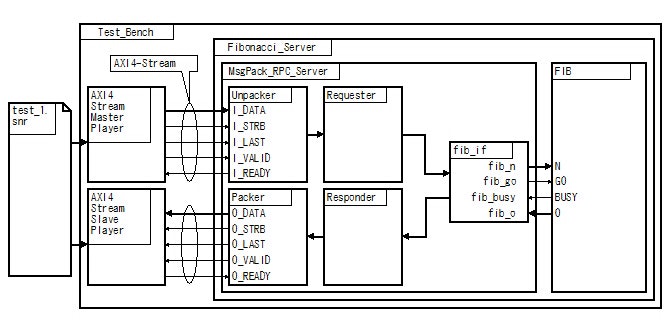

ブロック図

AXI4_Stream_Master_Player、AXI4_Stream_Slave_PlayerはYAML形式のシナリオファイルを読み込んでAXI4-Stream I/F信号の入出力を行うためのDummy_Plugライブラリのコンポーネントです。

ソースコード

フィボナッチを求めるjavaのソースコードです。kazunori279さんのフィボナッチをFPGAで書いてみたを参考にしました。

public class Fib {

public long fib(int n) {

long cur = 0;

long next = 1;

for (int i = 0; i < n; ++i) {

long tmp = cur;

cur = next;

next += tmp;

}

return cur;

}

}

手順

リポジトリと各submodule をダウンロード

shell% git clone git://github.com/ikwzm/msgpack-vhdl-examples.git

shell% cd msgpack-vhdl-examples

shell% git submodule init

shell% git submodule update

Fib.javaを高位合成

shell% export SYNTHESIJER=~/work/synthesijer/synthesijer/bin

shell% cd examples/fibonacci/src/main/synthesijer

shell% make

なお、SYNTHESIJER にはsynthesijerをインストールしているパスをしてください。

テストシナリオの作成

AXI4_Stream_Master_PlayerおよびAXI4_Stream_Slave_Player用のテストシナリオを作ります。

shell% cd examples/fibonacci/src/test/scenarios

shell% ruby test_1.rb

test_1.rb はテストシナリオ(YAML形式)を生成するためのrubyスクリプトです。

Vivado プロジェクトの作成

Vivado プロジェクトを作成するためのTclファイル(create_project.tcl)を用意しています。

Vivadoを起動して次のメニューからTclファイルを実行してください。

Vivado > Tools > Run Tcl Script... > examples/fibonacci/sim/vivado/synthesijer/create_project.tcl

シミュレーションを実行

Vivado プロジェクトを開き、次のようにシミュレーションを実行してください。

Vivado > Flow > Run Simulation > Run Behavioral Simulation

参照

- MessagePack for VHDL (https://github.com/ikwzm/msgpack-vhdl)

- MessagePack for VHDL Examples (https://github.com/ikwzm/msgpack-vhdl-examples)

- MessagePack-RPCを使ってFPGAを制御

- フィボナッチを求める回路をVHDLとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)

- フィボナッチを求める回路をPolyphonyとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)

- フィボナッチを求める回路をSynverllとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)

- フィボナッチを求める回路をneonlightとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)