はじめに

shtaxxxさんのブログ「Pythonベースの高位合成コンパイラPolyphonyを試してみた」でフィボナッチをPythonで記述してPolyphonyという高位合成ツールでVerilog-HDLにするという記事を見て、これは是非とも試してみねばなるまいと思ってやってみました。

用意するもの

- Xilinx Vivado 2015.3

- polyphony

- Ruby 1.9.3 以降

- msgpack-vhdl-examples

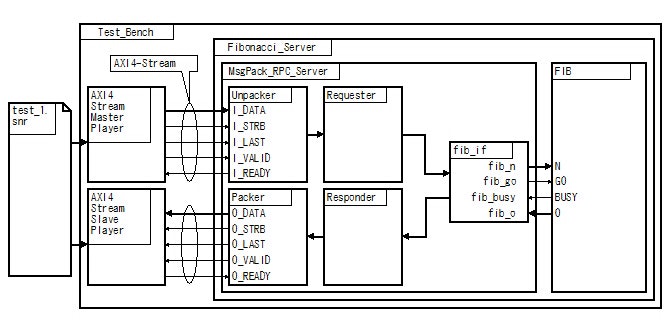

ブロック図

ソースコード

フィボナッチを求めるpythonのソースコードです。「Pythonベースの高位合成コンパイラPolyphonyを試してみた」のものをそのまんま使わせてもらいました。

def fib(n):

if n <= 0: return 0

if n == 1: return 1

r0 = 0

r1 = 1

for i in range(n-1):

prev_r1 = r1

r1 = r0 + r1

r0 = prev_r1

return r1

手順

リポジトリと各submodule をダウンロード

shell% git clone git://github.com/ikwzm/msgpack-vhdl-examples.git

shell% cd msgpack-vhdl-examples

shell% git submodule init

shell% git submodule update

fib.pyを高位合成

shell% cd examples/fibonacci/src/main/polyphony

shell% polyphony -o fib fib.py

polyphonyはこちらからダウンロードしてください。

詳しくは「Pythonベースの高位合成コンパイラPolyphonyを試してみた」を参照してください。

テストシナリオの作成

すでに作成済みのテストシナリオ(examples/fibonacci/src/test/scenarios/test_1_32.snr)を用意しています。このテストシナリオを使う場合は、以下の点順は飛ばしてください。

AXI4_Stream_Master_PlayerおよびAXI4_Stream_Slave_Player用のテストシナリオを作ります。

shell% cd examples/fibonacci/src/test/scenarios

shell% ruby test_1_32.rb

test_1_32.rb はテストシナリオ(YAML形式)を生成するためのrubyスクリプトです。

Vivado プロジェクトの作成

Vivado プロジェクトを作成するためのTclファイル(create_project.tcl)を用意しています。

Vivadoを起動して次のメニューからTclファイルを実行してください。

Vivado > Tools > Run Tcl Script... > examples/fibonacci/sim/vivado/polyphony/create_project.tcl

シミュレーションを実行

前節で作った Vivado プロジェクトを開き、次のようにシミュレーションを実行してください。

Vivado > Flow > Run Simulation > Run Behavioral Simulation

結果

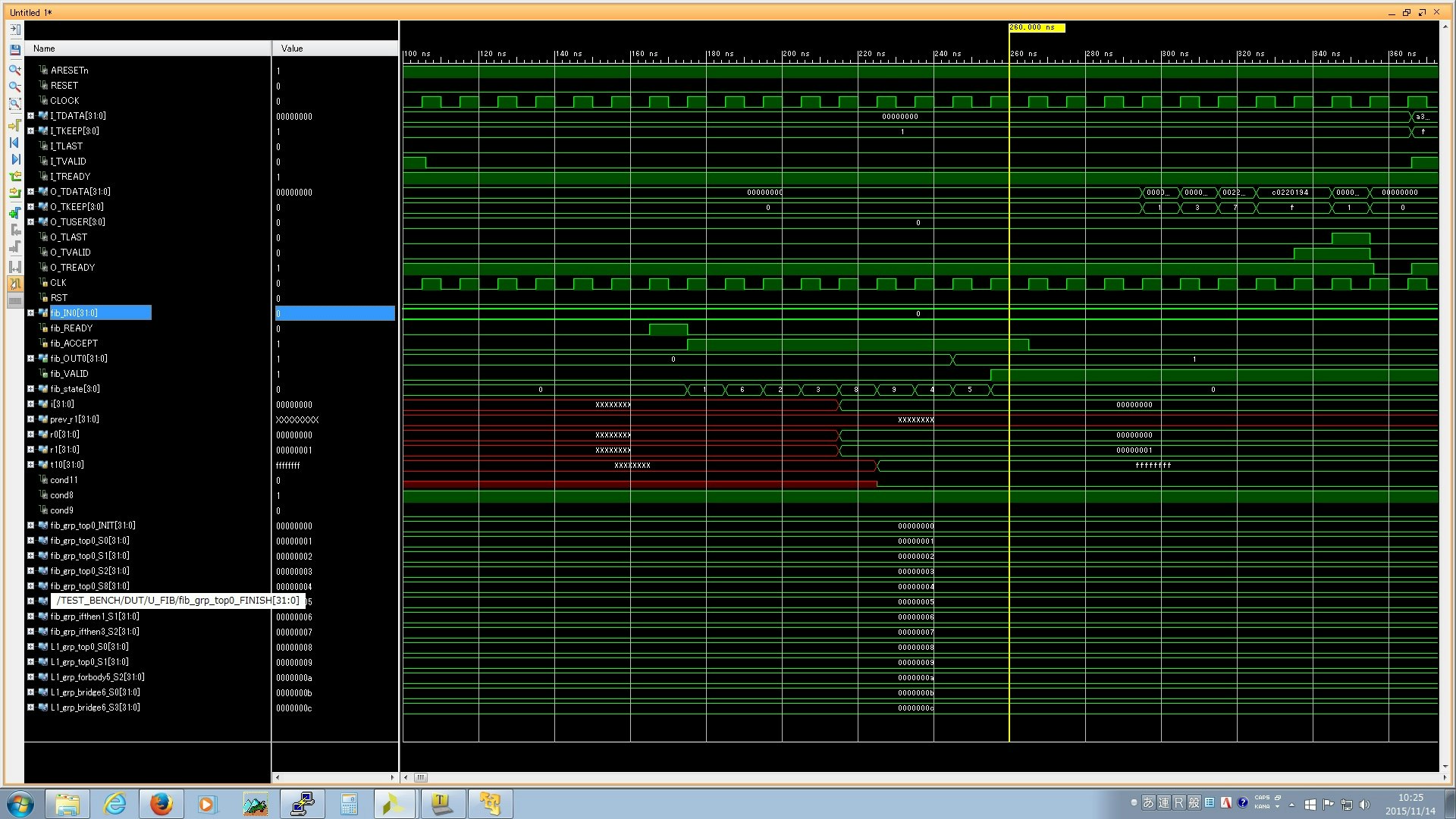

とりあえずシミュレーションすることは出来ました。

演算のビット幅を64ビットにする方法がわからなかったので、結果が32ビットに収まる範囲のnでしか計算していません。

何故かn=0の時の結果が0じゃなく1になってしまいますが、それ以外は正しい結果を返しているようです。

ちなみに、n=0の時の波形は下図のようになりました。

レジスタの一部がリセット後も不定になっているのもちょっと気になりますね。

参考

- polyphony

- Pythonベースの高位合成コンパイラPolyphonyを試してみた

- msgpack-vhdl-examples

- フィボナッチを求める回路をVHDLとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)

- フィボナッチを求める回路をSynthesijerとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)

- フィボナッチを求める回路をSynverllとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)

- フィボナッチを求める回路をneonlightとMessagePack-RPCでFPGAに実装してみた(シミュレーション編)