こんにちは。

使っているDE0-Nanoのクロックが50MHzであるため、出せるパルスの幅は20ナノ秒が下限と思っていたが違いました。

FPGAに搭載のPLL(Phase Locked Loop 位相同期回路)というものを利用すれば、入力周波数をn倍できるのだそうです。

いったいどんな魔法なのか理屈がさっぱりわかりませんが、とりあえず今日はこれを利用して2倍の100MHzのクロックをつくってみました。

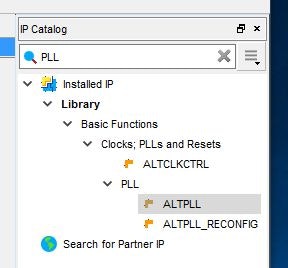

まずQuartus Prime Lite Edition(自分のバージョンは16.0)の「Tools」→「IP Catalog」を選択します。

画面の右端にIP Catalogの検索ボックスが表示されるので、「PLL」と入力します。

すると「ALTPLL」という項目が現れるのでダブルクリック。

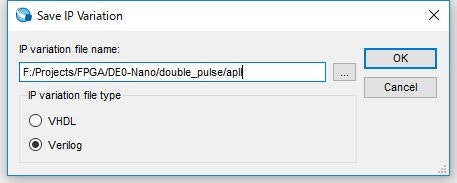

「Save IP Variation」というダイアログが表示されます。

「IP variation file name:」の値はプロジェクトフォルダに続けて自分は「apll」と入力しました。

(ALTPLLとかPLLと入力したら、その名前は使えないと怒られたので)

「IP variation file type:」は「Verilog」を選択しました。

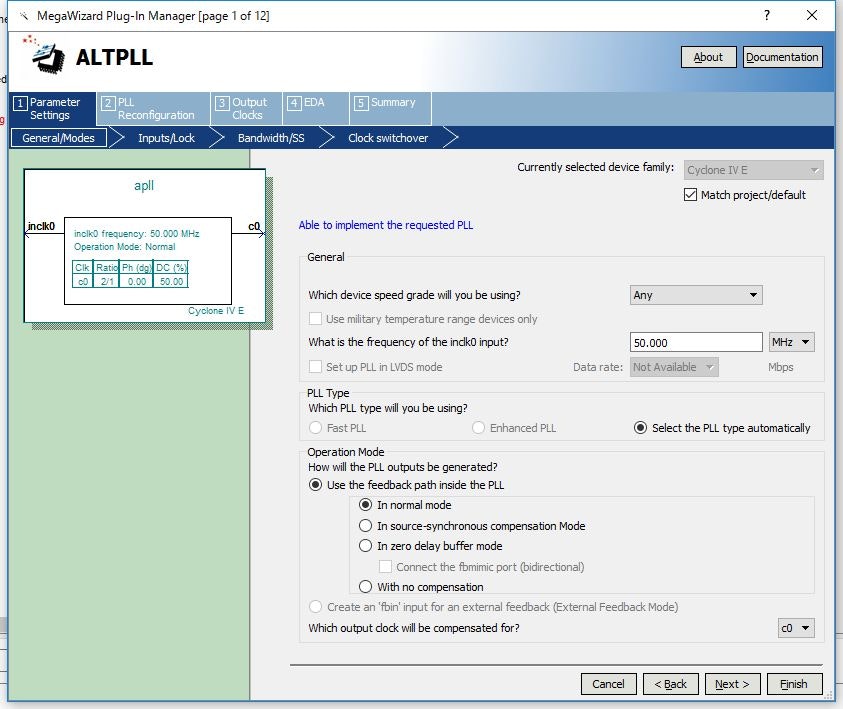

すると「MegaWizard Plug-In Manager」というウィザードが始まります。

最初の画面でもうわからなくて困りましたが、とりあえず「inputは何MHzなの?」と聞かれているのはわかるので「50MHz」と答えて「Next」をクリックしておきました。

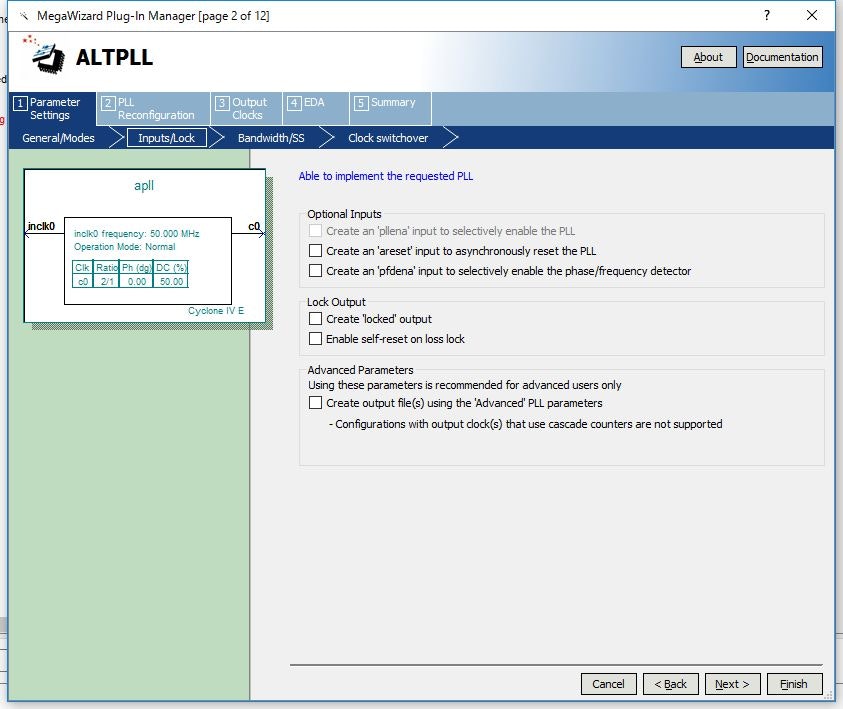

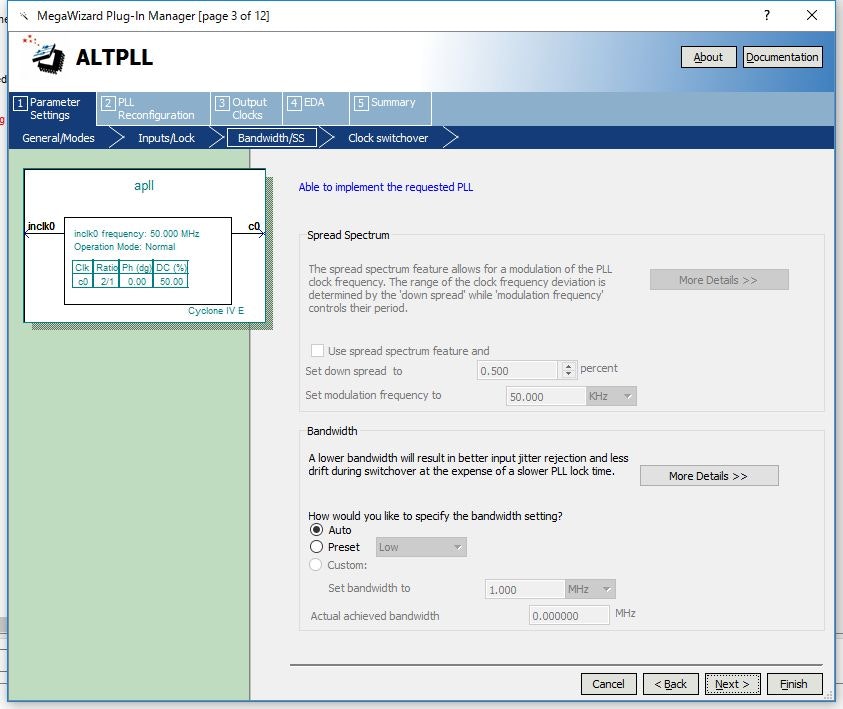

次の画面。

なにも答えられないので、すべてチェックのついていない状態で「Next」をクリック。

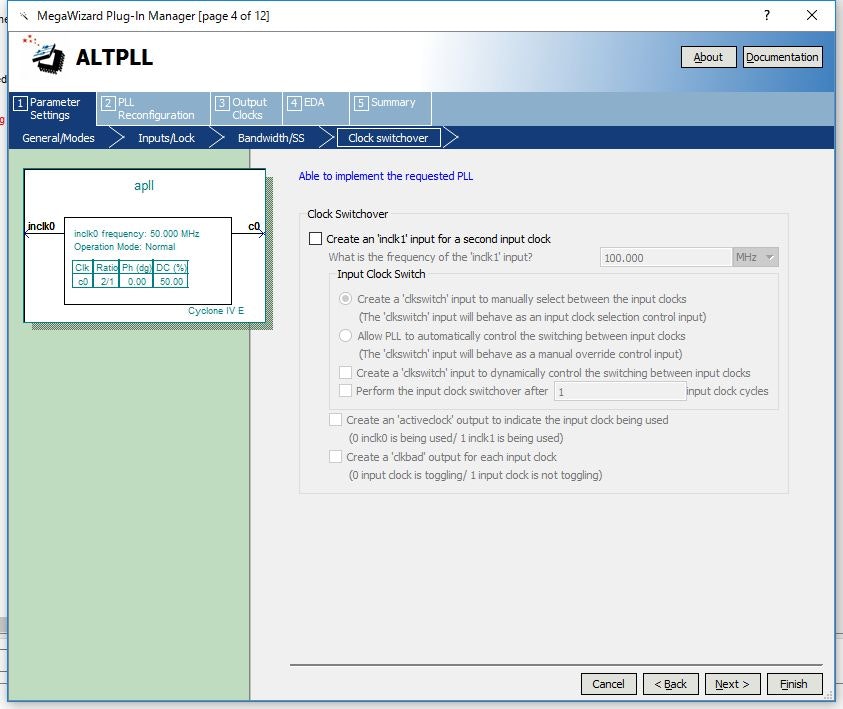

次の画面。

なにも触らず「Next」をクリック。自分の不勉強が情けなくなってきます。

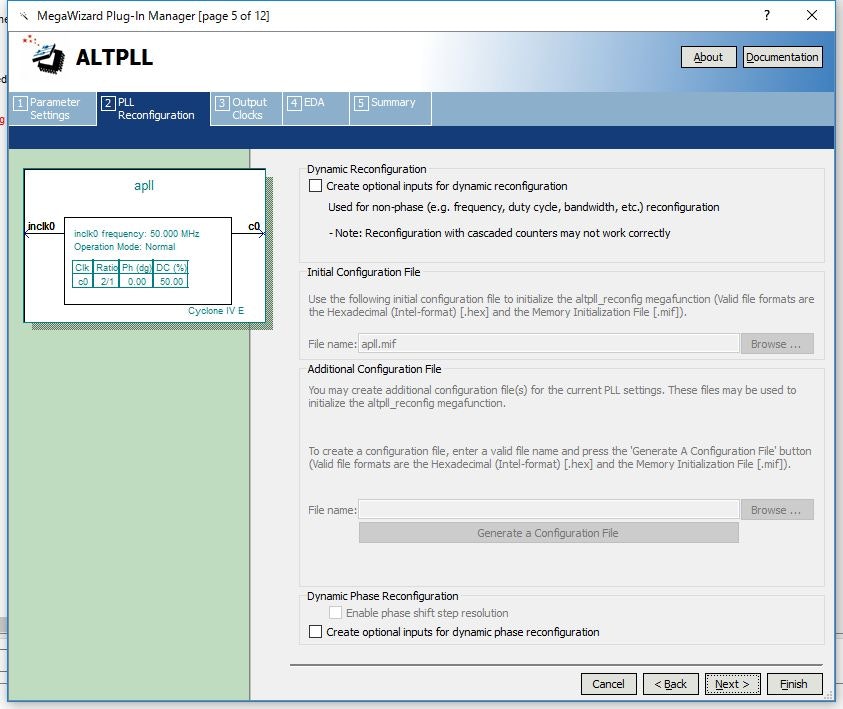

もう何も言うことはありません。

・・・。

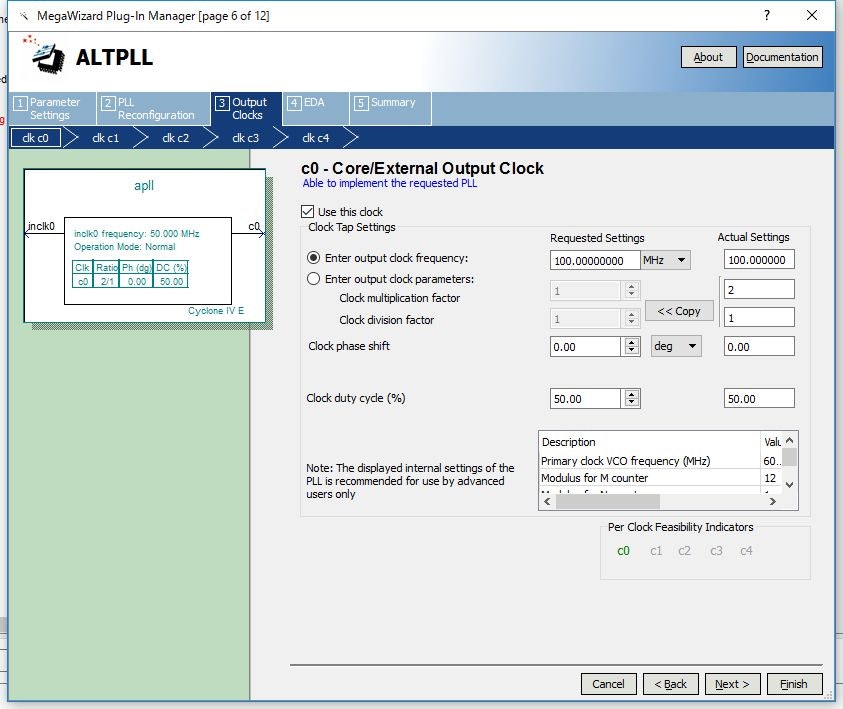

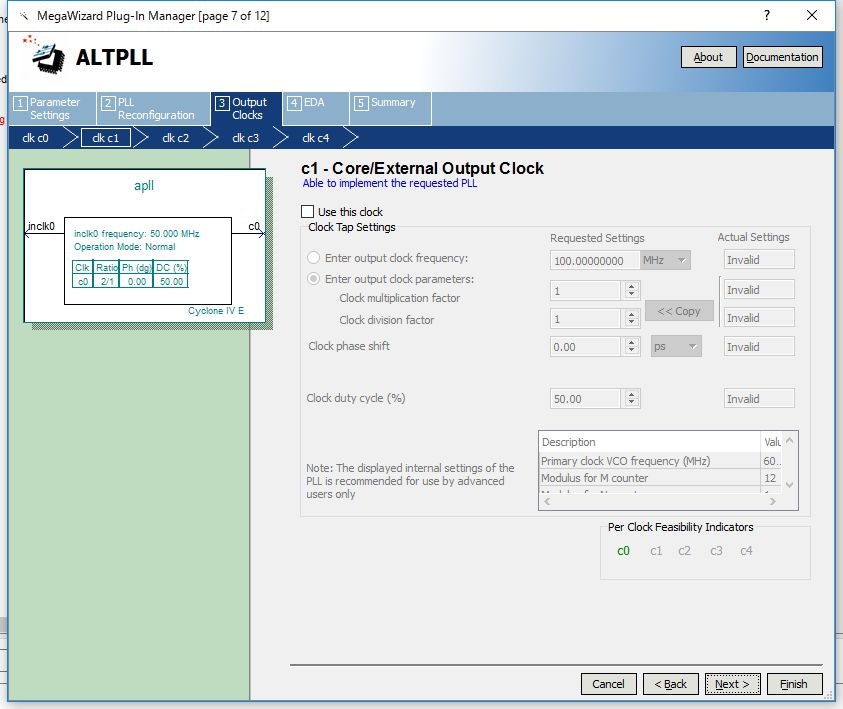

これは重要そうな予感がします!

「何MHzのクロックを作りたいの?」と聞かれている気がしたので「100MHzです!」と答えて「Next」をクリックしておきました。

まだまだクロックを作れるような感じですが、今はひとつあれば十分なので「Use this clock」のチェックが外れていることを確認しつつ「Next」をクリック。

clk4まで同じことを繰り返します。

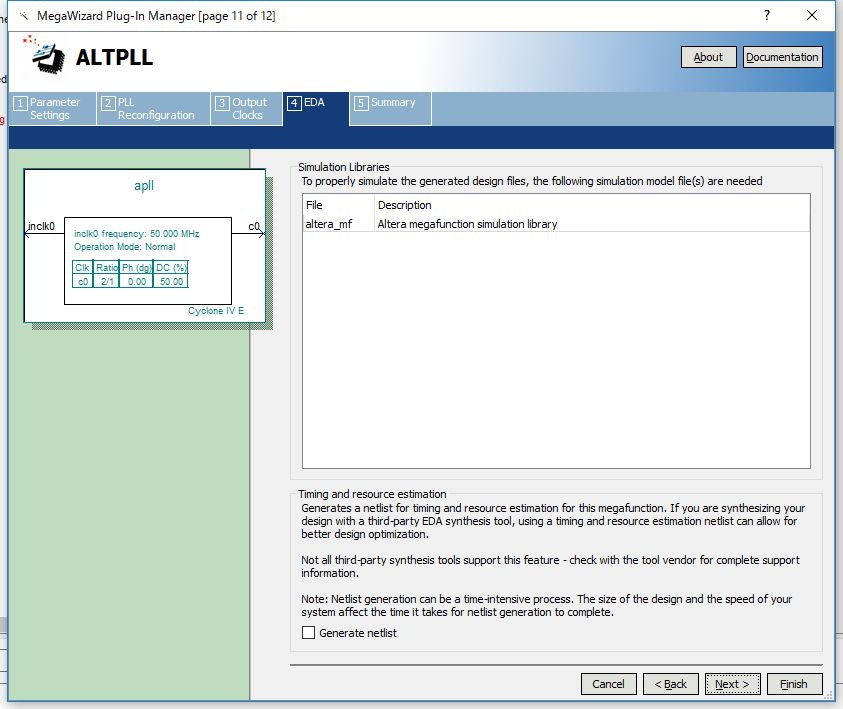

なにも変更せずに「Next」をクリック。

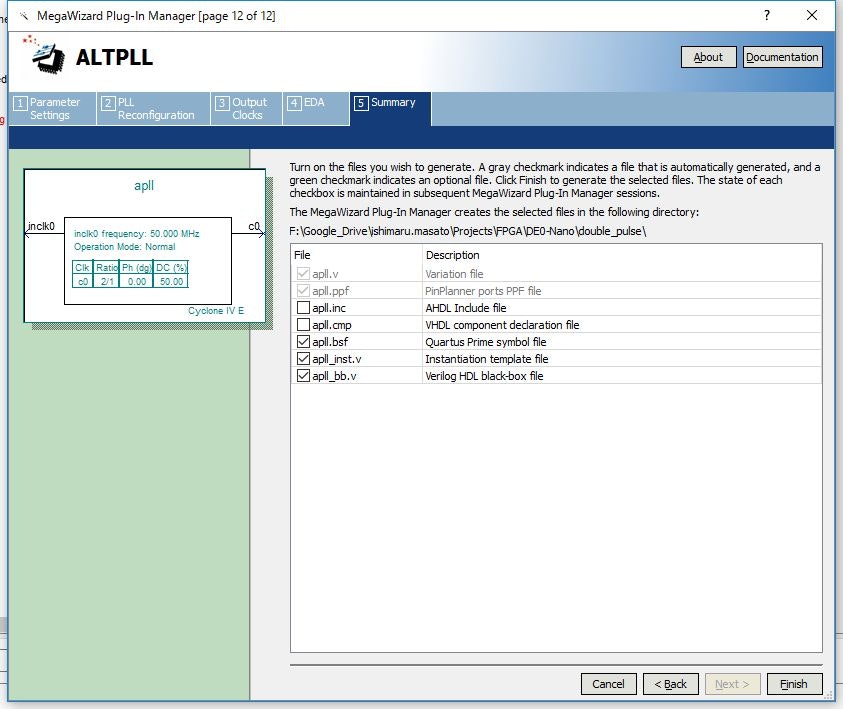

ついに最後の画面。

なにやら出力するファイルの確認のようです。特になにもいじらずに「Finish」をクリックします。

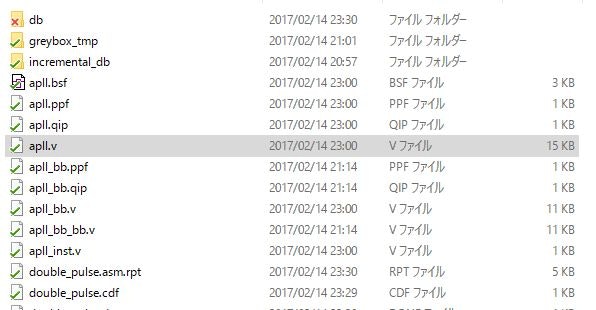

さて、エクスプローラーでプロジェクトフォルダを開いてみると、最初に入力した「apll」をファイル名に含むファイルがいくつか保存されていました。

その中でも「apll.v」というファイル。これはモジュールだろうと目星をつけました。

「たしかモジュールは関数のようなものだったはず・・・」

「50MHzクロックを入力すると100MHzクロックが出るように設定したはず・・・」

「てことは、引数にCLOCK_50を指定して呼び出せばいいのかな?」

と、いろいろと憶測を交えながら以下のリストのようなVerilogコードをでっち上げました。

module double_pulse(CLOCK_50, GPIO);

input CLOCK_50;

output [33:0] GPIO;

apll apll_inst(CLOCK_50, CLOCK_100);

assign GPIO[3] = CLOCK_100;

endmodule

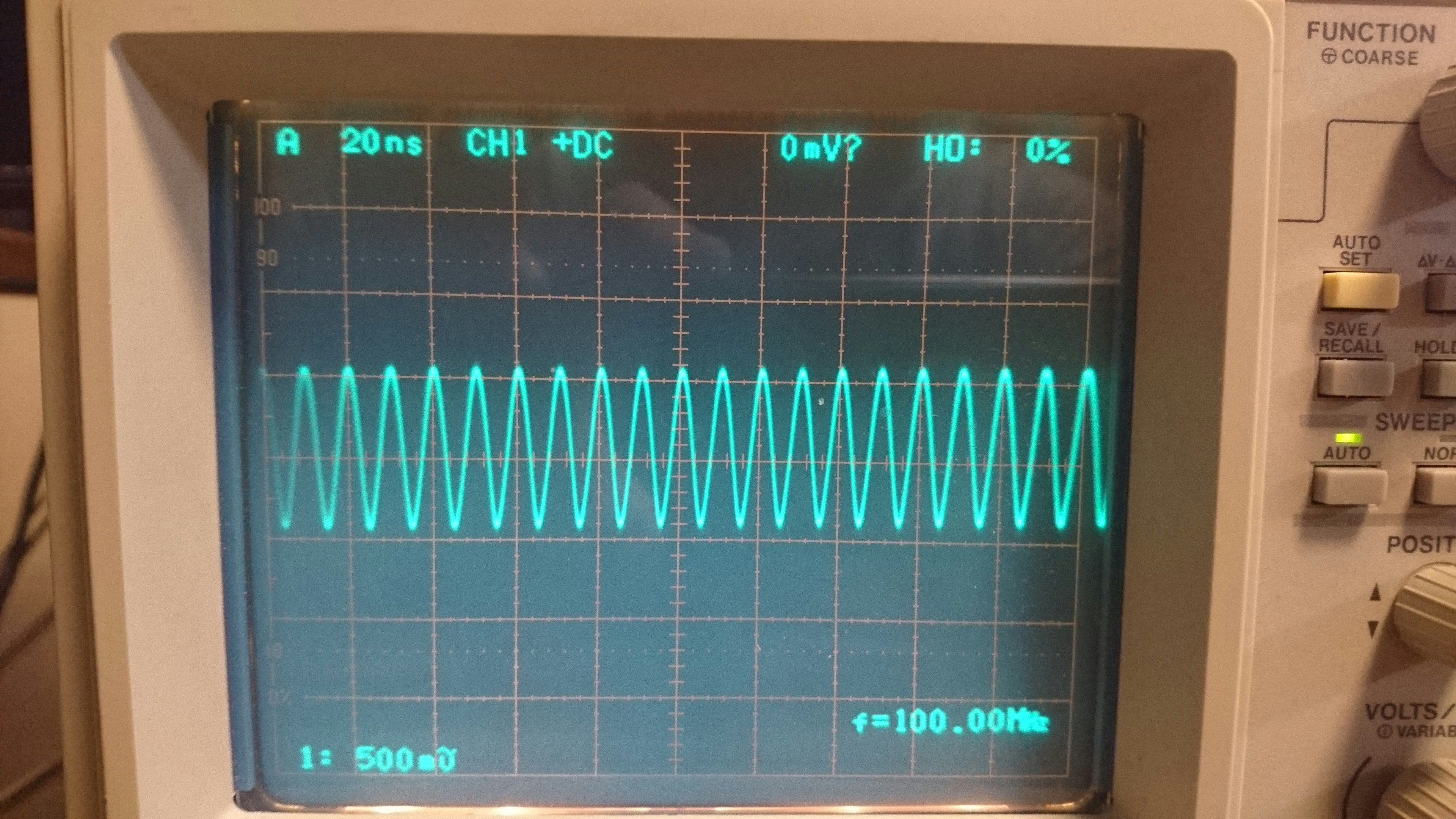

結果・・・うまいこと100MHzのクロックを得ることができました!

わーい。