話題のズンドコを(無理|投げ)やりにVerilogで実装。

方針

ズン、ドコの入力は1bit幅のzundoko信号により扱う。

zundokoの生成は外部に任せる。

ズンを0、ドコを1として、クロック立ち上がりで読む。

読んだ入力はシフトレジスタに詰めて、

5'b00001になったらkiyoshi信号をアサートする。

コード

zundoko.v

module ZundokoChecker(

input clk,

input rst,

input zundoko,

output reg kiyoshi

);

localparam Zun = 1'b0;

localparam Doko = 1'b1;

localparam [4:0] SR_Initial = {Doko,Doko,Doko,Doko,Doko};

localparam [4:0] Target = {Zun,Zun,Zun,Zun,Doko};

reg[4:0] sr;

wire[4:0] sr_next = {sr,zundoko};

always @(posedge clk or posedge rst) begin

if (rst) begin

sr <= SR_Initial;

end

else begin

sr <= sr_next;

end

end

always @(posedge clk or posedge rst) begin

if (rst) begin

kiyoshi <= 1'b0;

end

else if(sr_next == Target) begin

kiyoshi <= 1'b1;

end

end

endmodule

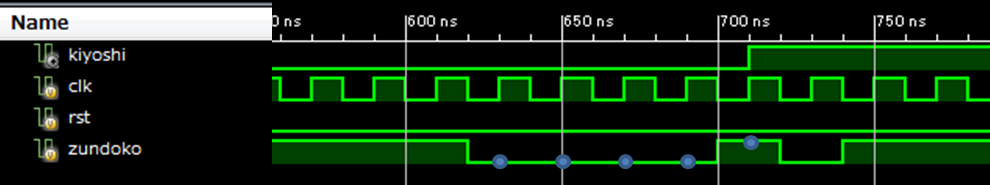

シミュレーション

とりあえずzundokoをシミュレーションで与える。

zundokoTest.v

module ZundokoTest;

reg clk;

reg rst;

reg zundoko;

wire kiyoshi;

ZundokoChecker uut (

.clk(clk),

.rst(rst),

.zundoko(zundoko),

.kiyoshi(kiyoshi)

);

always #10 begin

clk <= ~clk;

end

always @(negedge clk ) begin

zundoko <= $random & 1'b1;

end

initial begin

clk = 0;

rst = 1;

zundoko = 0;

#100;

rst <= 0;

end

endmodule