はじめに

Synthesijerで作ったモジュールをMessagePack-RPCで制御する(IP-Package編)の続きです。

今回は、前回作ったIP(Accumulator_Server)を Xilinx社のFPGA(ZYNQ)用に論理合成する手順を説明します。

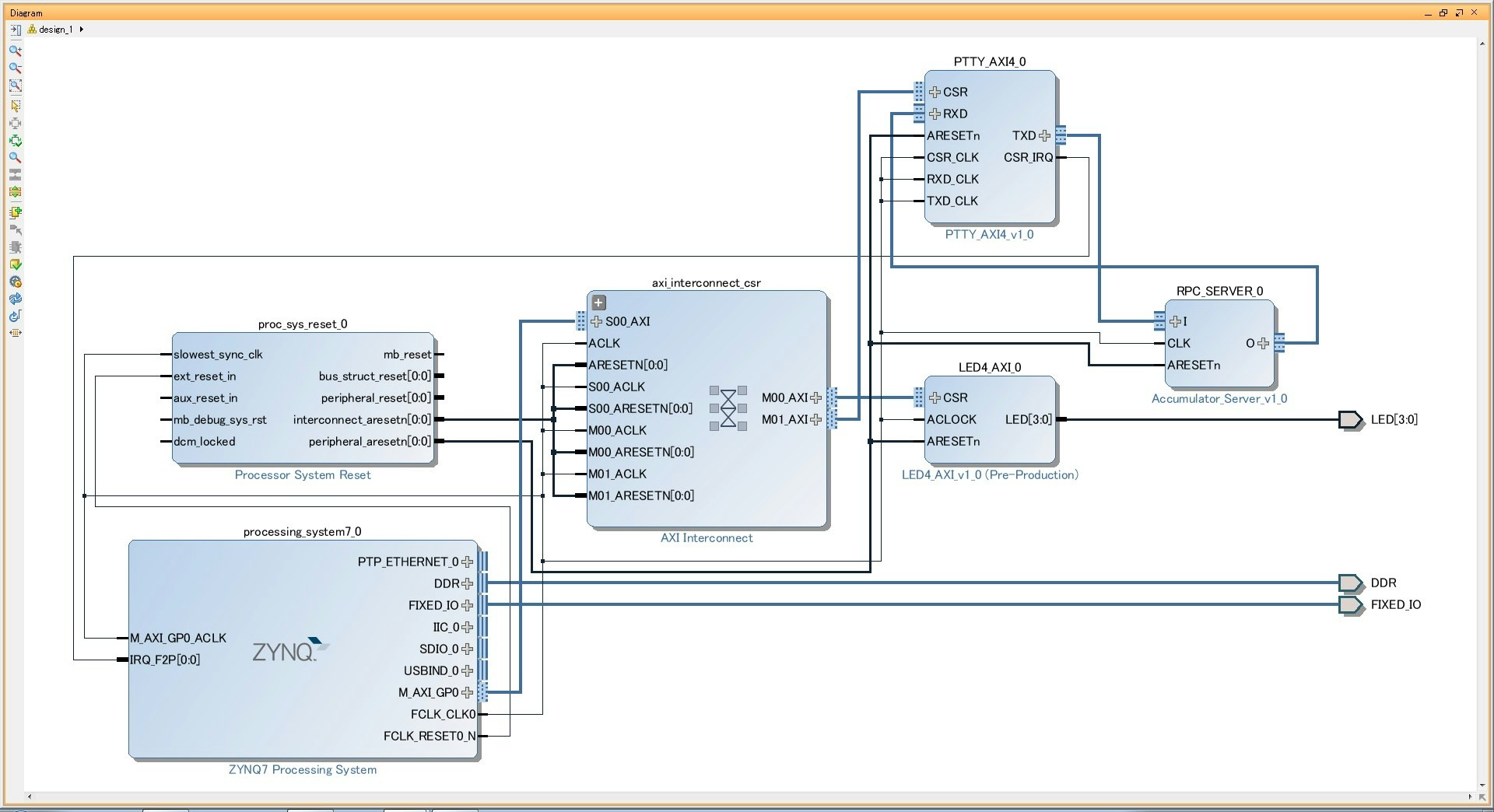

ここでは次のようなデザインを例に手順を示します。

開発環境

プロジェクトのリポジトリ

開発ツール

- Xilinx Vivado 2015.3 or 2015.4

- Xilinx SDK 2015.3 or 2015.4

必要なIP

- Accumulator_Server : 前回作ったMessagePack-RPC-Server + Accumulator

- PTTY_AXI : CPU-Accumulator_Server間の通信用IP PTTY_AXI (https://github.com/ikwzm/PTTY_AXI)

- LED_AXI : ZYNQのLED制御用IP LED_AXI (https://github.com/ikwzm/LED_AXI)

デザインフロー

githubからリポジトリをダウンロード

shell% git clone git://github.com/ikwzm/msgpack-vhdl-examples.git msgpack-vhdl-examples

shell% cd msgpack-vhdl-examples

githubからサブモジュールをダウンロード

shell% git submodule init

shell% git submodule update

プロジェクトを作る

examples/accumulator/fpga/xilinx/zybo_test_1/projectにVivado用のプロジェクトを作ります。

プロジェクト生成用のTclスクリプト(create_project.tcl)を用意しているので、Vivado で動かします。

Tclスクリプトを Vivado のバッチモードで動かす場合は次のようにします。

shell% cd examples/accumulator/fpga/xilinx/zybo_test_1/project

shell% vivado -mode batch -source create_project.tcl

Tclスクリプトを Vivado のGUIモードから動かす場合は次のようにします。

Vivado > Tools > Run Tcl Script... > examples/accumulator/fpga/xilinx/zybo_test_1/project/create_project.tcl

論理合成~配置配線~ビットストリームファイル作成まで

論理合成~配置配線~ビットストリームファイル作成までを行うTclスクリプト(implementation.tcl)を用意しています。

Tclスクリプトを Vivado のバッチモードで実行する場合は次のようにします。

shell% vivado -mode batch -source implementation.tcl

Tclスクリプトを使わずにVivado の GUI からビットストリームを生成するには次のようにします。

Vivado > Flow Navigator > Run Synthesis

Vivado > Flow Navigator > Run Implementation

Vivado > Flow Navigator > Generate Bitstrem

SDKのためにハードウェア情報をエクスポートする.

ハードウェア情報をエクスポートするTclスクリプト(export_hardware.tcl)を用意しています。

Tclスクリプトを Vivado のバッチモードで実行する場合は次のようにします。

shell% vivado -mode batch -source export_hardware.tcl

Tclスクリプトを使わずにVivado の GUI からハードウェア情報をエクスポートするには次のようにします。

Vivado> File > Export > Export Hardware > Export to: > OK

これで project/project.sdk/design_1_wrapper.hdf が出来ます.

FSBL(First Stage Boot Loader)を生成する.

FSBLを生成するTclスクリプト(build_fsbl.tcl)を用意しています。

Tclスクリプトを Vivado SDK のバッチモードで実行する場合は次のようにします。

shell% xsdk -batch -source build_fsbl.tcl

Tclスクリプトを使わずにVivado SDK の GUI からFSBLを生成するには次のようにします。

SDKを起動する.

Vivado> File > Launch SDK > Exported location: Workspace: > OK

アプリケーションプロジェクトを作る.

SDK> File > New > Aplication Project

次のようなウインドウがポップするので Project name と Template を入力.

New Project

Project name: fsbl <- 入力

Target Hardware

Hardware Platfrom: design_1_wrapper_hw_platform_0 <- 最初から選択されている

Processor: ps7_cortexa9_0 <- 最初から選択されている

Target Software

Language: C <- 最初から選択されている

OS Platform: standalone <- 最初から選択されている

Board Support Package: Create New fsbl_bsp <- Project Nameを入力すると自動的に入力される

Template: Zynq FSBL <- 選択(この項目は次の(NEXT>)タグを押すと出てきます)

Finishボタンを押すと自動的に project/project.sdk/fsbl/Debug/fsbl.elf が生成されます.

u-bootを生成する.

このプロジェクトでは u-boot の作成は行いません. とりあえず適当に作った u-boot.elf を ./boot に入れておきました.

BOOT.binを生成する.

Xilinx社のツールが起動するシェル環境(Vivado Tcl Shellなど)で次のコマンドを入力.

shell% cd boot/

shell% bootgen -image u-boot.bif -w on -o BOOT.bin

参照

MessagePack for VHDL (https://github.com/ikwzm/msgpack-vhdl)

MessagePack for VHDL Examples (https://github.com/ikwzm/msgpack-vhdl-examples)

MessagePack-RPCを使ってFPGAを制御

Synthesijerで作ったモジュールをMessagePack-RPCで制御する(アーキテクチャ編)

Synthesijerで作ったモジュールをMessagePack-RPCで制御する(IP-Package編)

Synthesijerで作ったモジュールをMessagePack-RPCで制御する(TTYドライバ編)

Synthesijerで作ったモジュールをMessagePack-RPCで制御する(MessagePack-Ruby編)

Synthesijerで作ったモジュールをMessagePack-RPCで制御する(リモートサーバー編)